سلام به همه همراهان مایکروالکام. همون طور که در جریان هستید در این سری از مطالب سعی میکنم تمام مقدمات لازم برای طراحی و شبیه ساز حافظه های DDR (حافظه های DDR3 و DDR4) را با شما در میان بگذارم. پس با من تا انتهای مطلب همراه باشید. همچنین شما میتویند سایر مطالب من رو از این لینک و یا آدرس Linkedin من مطالعه و مورد نقد و بررسی قرار بدید. خوشحال می شم هم از طریق Comment ذیل این پست و هم از طریق Email و Linkedin با من در ارتباط باشید.

مقدمه

مطالبی که در این قسمت به آن پرداخته خواهد شد شامل موراد زیر است.

- مفهوم دیگری در Timing سیگنال های DDR رو بیان میکنم که عملا بدون دونستن اون، تحلیل پاسخ ها و نمودار های زمان بندی در شبیه سای تراشه های DDR غیرممکن هست. لذا پیشنهاد میکنم این بحث رو با دقت مضاعف پیگیری کنید.

- در یک بحث تکمیلی، روش های محاسبات حجم حافظه و روش انتخاب تراشه مناسب DDR برای پردازنده Controller (مثل یک FPGA) رو بیان میکنم.

- در مورد حافظه SPD موجود در ماژول های SODIM و DIMM صحبت میکنیم و محتویات اون رو شرح خواهم داد.

یادآوری دسته بندی سیگنال های تراشه های DDR

برای مقدمه دسته های سیگنال مبتنی بر استاندارد JEDEC در حافظه های DDR در زیر بیان شده است.

- Data Group: Data Strobe DQS[0:8], Data Strobe Complement DQS[0:8],Data Mask [0:8], Data DQ[0:63], Clock Bits[0:7]

- Address and Command Group: Bank Address BA[0:2], Address A[0:15], Command Input RAS#,CAS# WE#

- Control Group: Chip Select CS[0:3], Clock Enable CKE[0:3], On-Die Termination ODT[0:3]

- Clock Group: Differential lock CK[0:5], CK#[0:5]

| DATA MASK | DATA STROBE COMPLEMENT | DATA STROBE | DATA |

| DM0 | DQS#0 | DQS0 | DQ[0:7] |

| DM1 | DQS#1 | DQS1 | DQ[8:15] |

| DM2 | DQS#2 | DQS2 | DQ[16:23] |

| DM3 | DQS#3 | DQS3 | DQ[24:31] |

| DM4 | DQS#4 | DQS4 | DQ[33:39] |

| DM5 | DQS#5 | DQS5 | DQ[40:47] |

| DM6 | DQS#6 | DQS6 | DQ[48:55] |

| DM7 | DQS#7 | DQS7 | DQ[63:56] |

| DM8 | DQS#8 | DQS8 | CB[0:7] |

مفاهیم نرخ داده، کلاک و پهنای باند در حافظه های DDR

در این حافظه ها همه چیز از فرکانس کلاک محاسبه میشود. برای مثال فرکانس Clock برای یک مجموعه حافظه DDR (با هر توپولوژی که دارد مثل Fly-By یا Clam-Shell)، اگر 200MHz باشد، نرخ داده دو برابر نرخ کلاک است و اگر بخواهیم پهنای باند آن را محاسبه کنیم، باید آن را در عرض باس داده (تعداد پین های داده مجموعه DDR) ضرب کرده و به 8 (عرض یک داده 8 بیتی یا به عبارتی عرض یک بایت) تقسیم کنیم تا عدد ما به Byte نرمالیزه شده و مشخص شود که مجموعه DDR ما، در هر ثانیه، چند بایت را در باس خود ارسال میکند.

:مثال

- Clock Frequency = 200MHz

- Data Rate = 400MT/s*

- Band Width = 40MT/s * 64 bits)/8 =3200 MB/S**

- *MT/s = Mega Transfer per Second

- **MB/S = Mega Byte per Second

پارامتر های چند DDR

در جدول زیر، پارامتر های چندین DDR از استاندارد های مختلف (DDR2 و DDR3 و DDR4) و عرض داده 64bit آورده شده است.

| Band Width (MB/S) | Data Rate (MT/S) | Clock Speed (MHz) | Standard |

| 3200 | 400 | 200 | DDR2-400 |

| 4266.67 | 533 | 266.67 | DDR2-533 |

| 6400 | 800 | 400 | DDR2-800 |

| 8533.33 | 1866.67 | 266.67 | DDR2-1066 |

| 6400 | 800 | 400 | DDR3-800 |

| 8533.33 | 16066 | 533.3 | DDR3-1066 |

| 14933.33 | 1866.67 | 933.33 | DDR3-1866 |

| 17066.67 | 2133.33 | 1067.67 | DDR3-2133 |

| 12800 | 1600 | 800 | DDR4-1600 |

| 14933.33 | 1866.67 | 933.33 | DDR4-1866 |

| 17066.67 | 2133.33 | 1067.67 | DDR4-2133 |

| 19200 | 2400 | 1200 | DDR4-2400 |

لذا رابطه بین Data Rate و Frequency یک حافظه DDR، به این صورت است که نرخ داده همواره دو برابر فرکانس کلاک حافظه است و باید دقت کرد که DQS ها، DQ ها و Clock با همین فرکانس کار میکنند. مثل همه تجهیزات، دوره تناوب برابر با معکوس فرکانس است. Unit Interval (که با UI شناخته میشود)، نصف دوره تناوب سیگنال است.

مثال

- اگر Data Rate = 800 MT/S باشد:

- Frequencyof Clock (fCLK) = Data Rate/2 = 800/2 = 400 MHz

- Clock Period (TCLK) = 1/fCLK – 1/400MHz = 2.5nS

Clock و سیگنال های DQS یک فرکانس کار میکنند. Bit Interval نصف Period کلاک است. فرکانس DQ ها اما برابر با همان فرکانس Clock است.

- Bit Inteval (DQ) = TCLK/2 =2.5 ns/2 = 1.25 ns

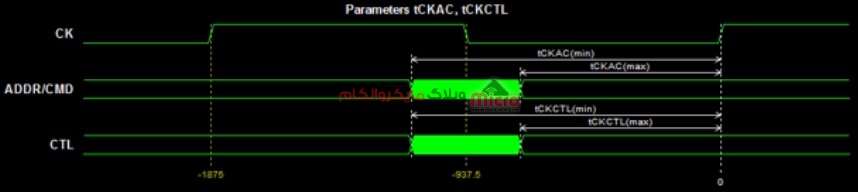

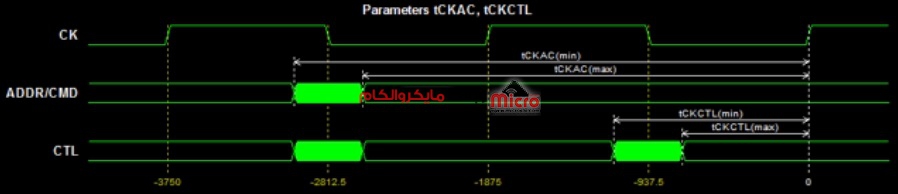

زمان بندی 1T و 2T

زمان بندی 1T و 2T فقط کاربرد در باس Address و Command دارد. در زمانبندی 1T، با اولین لبه بالارونده کلاک، پین های Address و Command، زمانبندی میشوند. در زمانبندی 2T ،Address و Command با دومین لبه کلاک، زمانبندی میشوند. توجه شود که در 2T، سیگنال های Control، همچنان نسبت به اولین لبه بالارونده Clock، زمان بندی میشوند.

- 1T Timing

- 2T Timing

محاسن و معایب 2T Timing

- بازدهی باس Address/Command را کاهش میدهد ولی در عوض، زمان Setup و Hold سیگنال را دو برابر کرده و دست طراح در آسودگی Routing را بازتر میکند.

- بطور مشخص، Setup و Hold سیگنال های Control هیچ فرقی نمیکند و هیچ مزیتی برای این سیگنال ها فراهم نمیکند.

پس یک موضوع کاملا مشخص است و آن این که از هر مدل زمانبندی Address/Command ای استفاده کنیم، UI دسته سیگنال های Address/Command ممکن است متفاوت باشد. در T1 Timing، سیگنال های Address/Command/Control، دارای UI برابر با نصف Period هستند. در T2 Timing، سیگنال های Address/Command دارای UI برابر یک period کامل و سیگنال های Contrl ای دارای UI برابر با نصف Period هستند.

- 1T Bit Interval (Add/Cmd/Ctrl) =TCLK = 2.5 nS

- 2T Bit Interval (Add/Cmd) =2 * TCLK = 5 nS

خلاصه

برای شبیه سازی حافظه DDR، نیاز داریم بدانیم UI سیگنال های DQ ،DQS ،Clock ،Address ،Command و Control چند ns است. برای دانستن مقدار UI باید بدانیم منظور از Frequency ،Data Rate و Bandwidth یک مجموعه DDR چیست. تا اینجا، به بررسی این مفاهیم پرداختیم و گفتیم که UI سیگنال های DQ ،DQD و Clock و Control برابر با Period÷2 بوده ولی برای سیگنال های Address و Command، بستگی به نوع زمانبندی آن ها در پیکربندی نرم افزاری DDR، مقدار UI متفاوت است.

- اگر زمانبندی 2T انتخاب شود، UI سیگنال های Address/Command برابر با Period خواهد بود و اگر 1T استفاده شود، UI سیگنال های Address/Command برابر با Period÷2 خواهد بود.

- این که کدام زمانبندی برای سیگنالهای Address/Command استفاده شود، به انتخاب برنامه نویس و طراح سخت افزار بستگی دارد و باید توجه داشت که هر کدام مزایا و معایب خود را دارد که در مورد آن مفصل توضیح داده شد.

انتخاب حافظه DDR مناسب

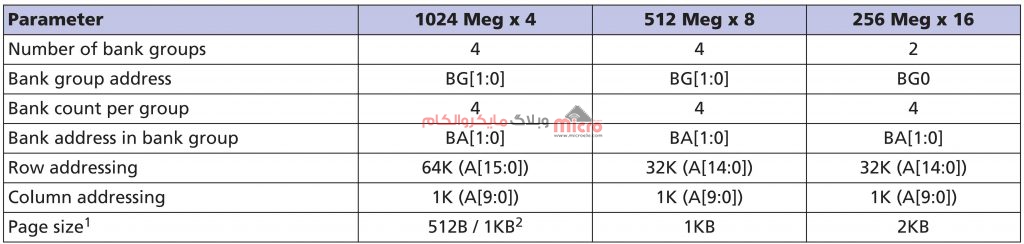

اندازه حافظه DDR بهصورت استاندارد و توسط کمیته استاندارد JEDEC تعیین میگردد. حافظههای Industrial با حجم بالا به سختی یافت میشوند. این بخش از استاندارد JESD79-4B استخراج شده است تا در انتخاب قطعه حافظه با میزان حافظه مشخص کمکرسان باشد.

همانطور که در جداول بالا مشخص است، یک پارامتر به نام Page Size در استاندارد JESD79-4B موجود است. در واقع این پارامتر، مشخصکننده تعداد بیتها در هر ردیف داده یا بهعبارتی دیگر برابر با تعداد بیتی است که در بخش Sense Amplifiers قرار میگیرد. لذا اگر آدرس ستون 10 بیتی باشد، هر ردیف 1024 بیت (1Kbit) است. برای یک قطعه 4X تعداد بیتهای آمده در بخش Sense Amplifiers یا بهعبارتی اندازه Page Size برابر با 4×1024=4Kbit است. به همین ترتیب برای 8X مقدار Page Size برابر با 8K bit است. لذا روش اندازهگیری میزان حافظه از روی جدول بالا برابر با فرمول زیر است:

میزان حافظه = تعداد گروه_بانکهای موجود در حافظه × تعداد بانکهای موجود در یک گروه × عرض ستونهای بانکها × تعداد ستونها(که از روی خط آدرس ستون بدست میآید) × تعداد ردیفها (که از روی تعداد خط آدرس ردیفها بدست میآید)

برای مثال برای یک حافظه 4Gb 4X داریم

- Number of Row Address bits: A0-A15 = 16 bits Total number of row = 2^16 = 64K

- Number of Column Address bits: A0-A9 = 10 bits Number of columns per row = 1K

- Width of each column = 4 bits

- Number of Bank Groups = 4

- Number of Banks = 4

- Total DRAM Capacity = 64K x 1K x 4 x 4 x 4 = 4Gb

بهعنوان مثال دوم به تراشه MT40A256M16 رجوع میکنیم. در برگه اطلاعات این تراشه جدول موجود در شکل زیر آورده شده است:

همانطور که میبینید در پیکربندی 256Meg X16 این تراشه دارای دو گروه_بانک بوده که در هرکدام چهار بانک موجود است. آدرسدهی سطرها 32کیلو و آدرسدهی ستونها یک کیلو هست. از طرفی عرض ستونها هم 16 است لذا حجم حافظه 2×4×32K×1K×16=8Mb یا معادل 1MB است. به زبان ساده، دو گروه داریم که هرکدام چهار بانک دارند و هر بانک 32K×1K عدد خانه با حجم 16 بیت دارد. لذا تعداد کل بیتهای حافظه 8Mb است.

توجه شود که تعداد خط آدرس روی تراشه به معنی این نیست که همه آنها در آدرسدهی سطرها شرکت میکنند یا همه آنها در آدرسدهی ستونها استفاده میشود. برای اینکه بفهمیم چه تعداد خط آدرس در آدرسدهی سطر و چه تعداد در آدرسدهی ستون استفاده میشود، باید به برگه اطلاعات تراشه حافظه و جداولی همانند شکل 15 در آن برگه اطلاعات مراجعه کرد.

معیار اول انتخاب حافظه: بر اساس عرض ستون (4X,8X,16X) و میزان حافظه انتخاب میگردد

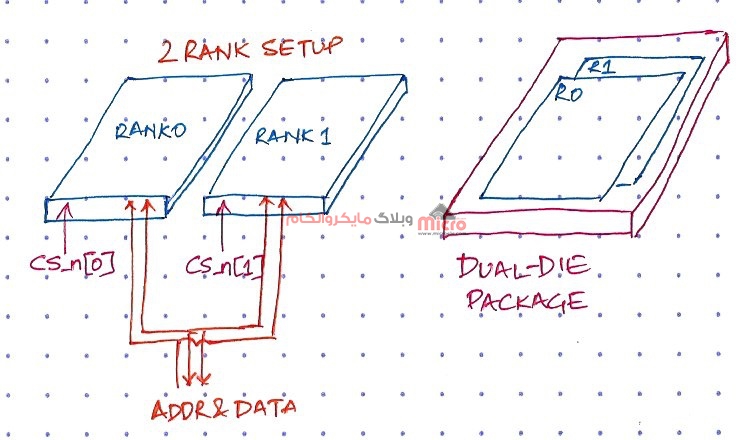

معیارهای مهم دیگر در انتخاب DDR4 آشنایی با عبارت Single-Rank، Dual-Rank، Quad-Rank و Dual-Die Package است. Rank بالاترین واحد منطقی است و برای افزایش ظرفیت حافظه مورد استفاده قرار میگیرد. اگر ما به حافظه DDR4 با ظرفیت 16Gb نیاز داشته باشیم به سه صورت میتوان عمل کرد. استفاده از یک تراشه 16Gb و یا استفاده از دو تراشه 8Gb و یا استفاده از چهار تراشه 4Gb که در حالت اول فقط یک خط داده و آدرس داریم ولی تراشه گرانتری را بر روی PCB قرار دادهایم.

در حالت دوم با استفاده از خطوط داده و آدرس مشترک و با استفاده از دو سیگنال انتخاب تراشه (Chip Select) CS-n کمی توسعه بورد را سختتر کرده ولی در عوض دو تراشه ارزانتر حافظه استفاده میکنیم. در حالت سوم هم با کاهش چشمگیر قیمت تراشه و استفاده از چهار CS-n میتوان قیمت تمامشده را بسیار کاست ولی توسعه PCB بسیار دشوارتر است. حالت اول را Single-Rank، حالت دوم را Dual-Rank و حالت سوم را Quad-Rank مینامیم.

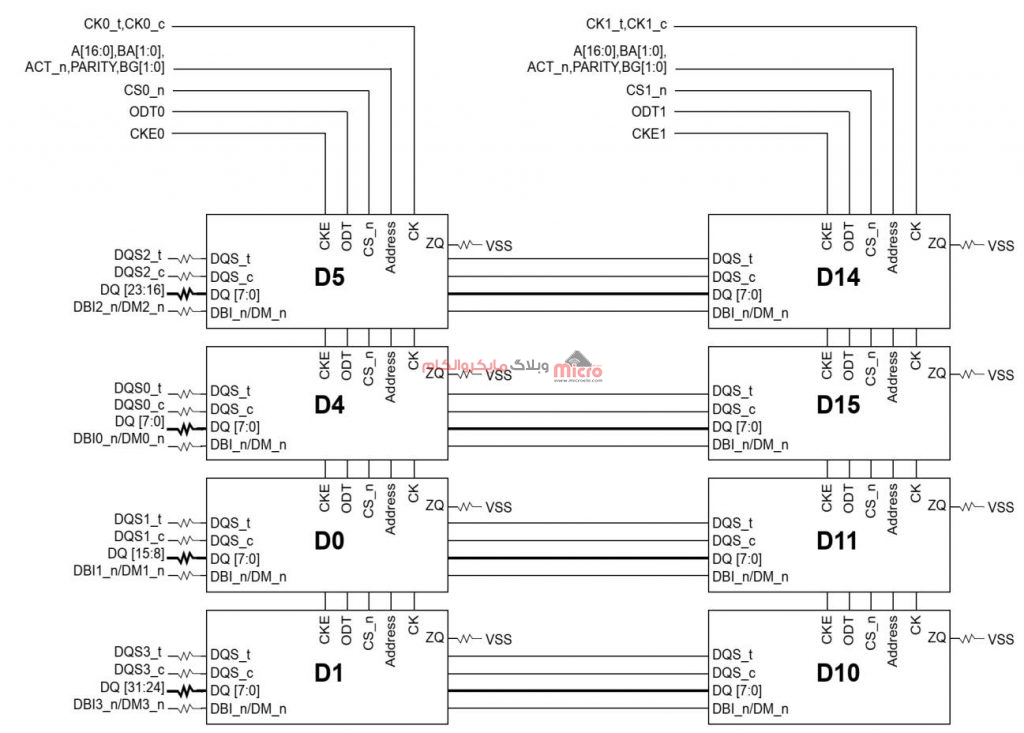

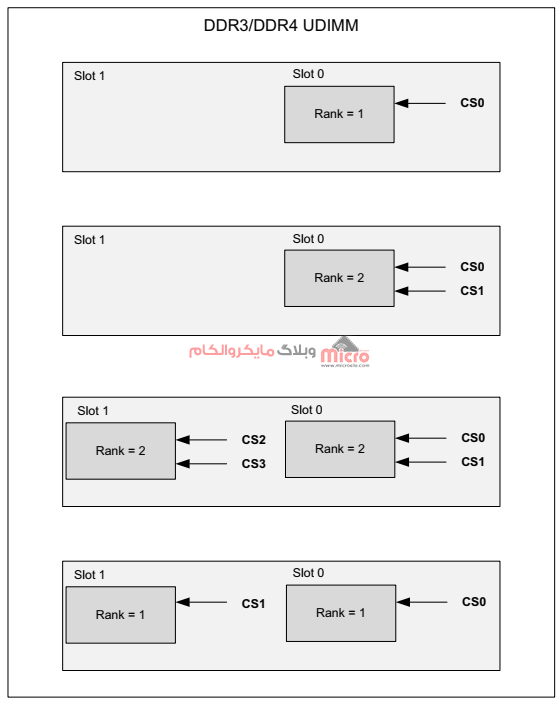

- لازم به ذکر است که در افزایش Rank یک حافظه، چهار دسته سیگنال به حافظه اضافه میگردد. این چهار دسته سیگنال عبارت اند از CS-n ،CLKE-n ،CLK-P,N و ODT-n که این سیگنالها بین Rank ها مشترک نبوده ولی دادهها و آدرسهای Rank ها باهم مشترک میباشند. برای تفهیم بهتر موضوع به دو شکل زیر، که مقایسه دو ماژول SODIMM با Rank یک و دو هست توجه بفرمایید.

مقایسه دو ماژول SODIMM با Rank

در توضیح ماژولهای DIMM مبتنی بر Quad Rank باید گفت که با توجه به اینکه جهت آگاهی از نحوه اتصالات پایهها درون این ماژولها مستندی در دسترس نبود، نمیتوان گفت که چرا باوجود اینکه پایههای CS-2,3 در کانکتور آنها وجود دارد، چرا بقیه پایههای لازم جهت افزایش Rank (مثل ODT-n و CLK_N,P و CLKE-n) برای Rank2,3 وجود ندارند. لذا این مورد و نحوه افزایش Rank به Quad Rank برای ما همچنان مجهول است. ولی از روی اسامی پایههای کانکتورهای استاندارد Quad Rank، حدس زده میشود که در حالت Quad Rank تنها نیاز به افزودن CS-2,3 بوده و بقیه پایهها (مثل ODT-n و CLK_N,P و CLKE-n) با Rank0,1 ، مشترک هستند.

خلاصه

بهطور خلاصه جهت افزودن Rank از حالت Single Rank به حالت Dual Rank، نیاز به افزودن چهار دسته سیگنال Cs-1 و ODT-1 و CLK1_N,P و CLKE-1 بوده ولی برای افزودن Rank از حالت Dual Rank به حالت Quad Rank، تنها کافی است دو سیگنال CS-2,3 به پایهها اضافه گردد.

Dual-Die Package یا DDP زمانی رخ میدهد که در واقع از حالت دوم استفاده کنیم ولی دو تراشه در یک تراشه توسعه دادهشده باشند. در این حالت برای هر Die موجود در تراشه یک CS مجزا، یک عدد CKE مجزا و یک عدد ODT مجزا خواهیم داشت. در شکل زیر تفاوت دو Rank مرسوم Dual-Die Package و Dual-Rank را مشاهده میکنید. در ضمن باید گفت برخی تراشهها نیز دارای چهار عدد Die در درون خود بوده که به آنها Quad-Die Package یا QDP میگوییم. نکته قابل تأمل این است که امکان استفاده از تراشههای DDP و QDP در درون ماژولهای RDIMM و LRDIMM صرفاً وجود دارد و در بقیه انواع DIMM ها این امکان وجود ندارد، چراکه امکان Stack کردن تراشهها وجود نداشته و در کانکتور بقیه انواع DIMM برای پایههای اضافهشده جهت DDP و QDP پایهای تعبیه نشده است.

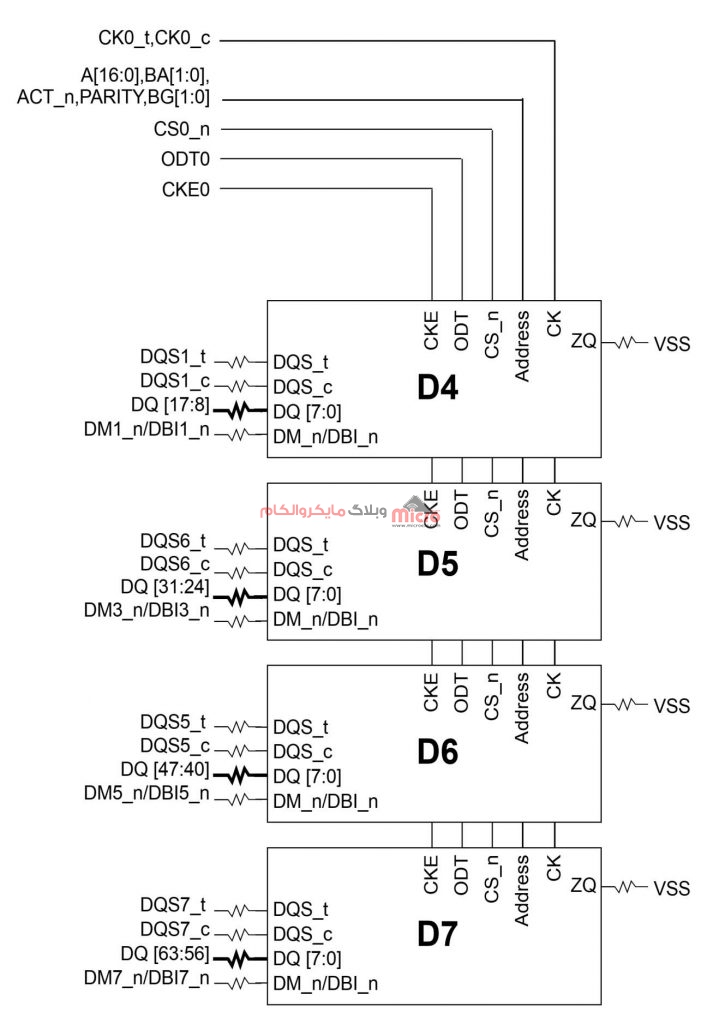

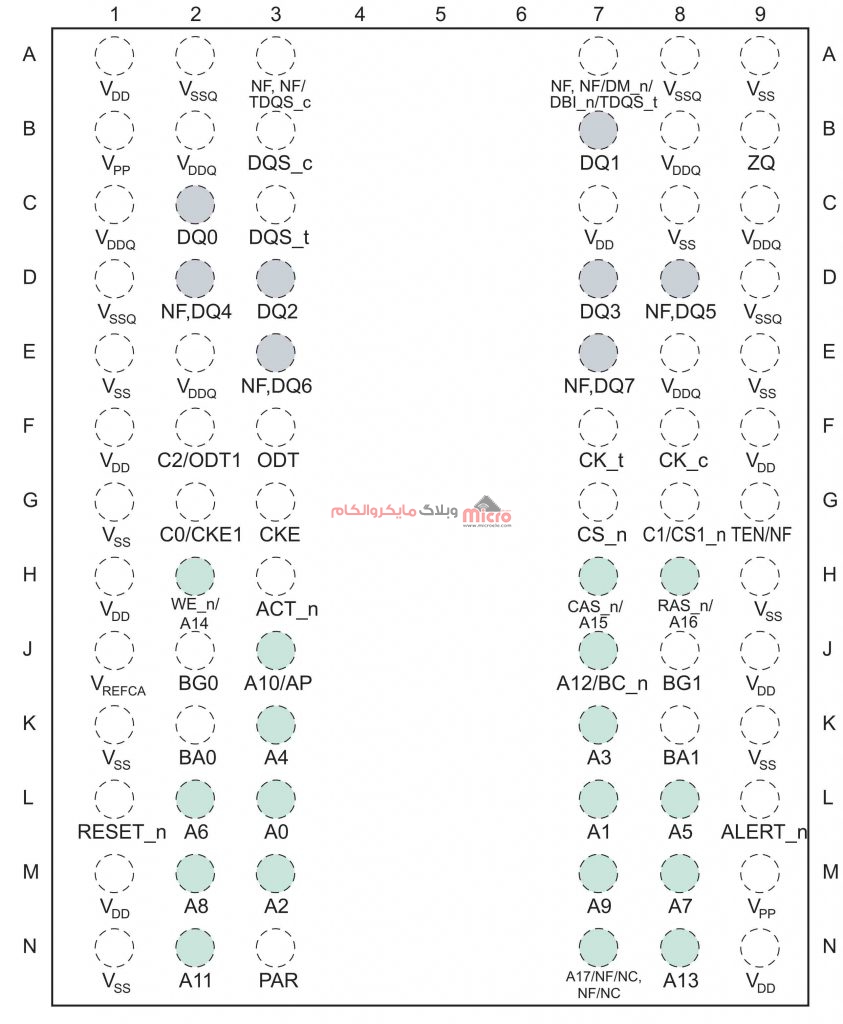

همانطور که در شکل زیر میبینید قطعه با شماره MT40A1G8 شرکت Micron که یک DDR4 از نوع DDP است، اعلام میکند که پایههای C0/CKE1,C1/CS1_n,C2/ODT1 جهت Stack کردن بکار برده میشوند و در برگه اطلاعات ماژول atf8c1gx64az شرکت Micron هم قید شده که C0/CKE1,C1/CS1_n,C2/ODT1 فقط در RDIMM و LRDIMM موجود میباشند.

همچنین در برگه اطلاعات قطعه MT40A1G8 و همانطور که در شکل 19 که یک Monolithic Package است قید شده که پایههای C0/CKE1,C1/CS1_n,C2/ODT1 صرفاً جهت Stack استفاده میشوند. علاوه بر این حرفی از DDP بودن آن نزده و در هیچ کجای برگه اطلاعات به وجه تمایز DDP و Monolithic اشاره نکرده است. لذا استنباط میشود که این قطعه Monolithic باشد، که در غیر این صورت به آن اشاره میشد.

معیار دوم انتخاب حافظه: بر اساس Rate حافظه است.

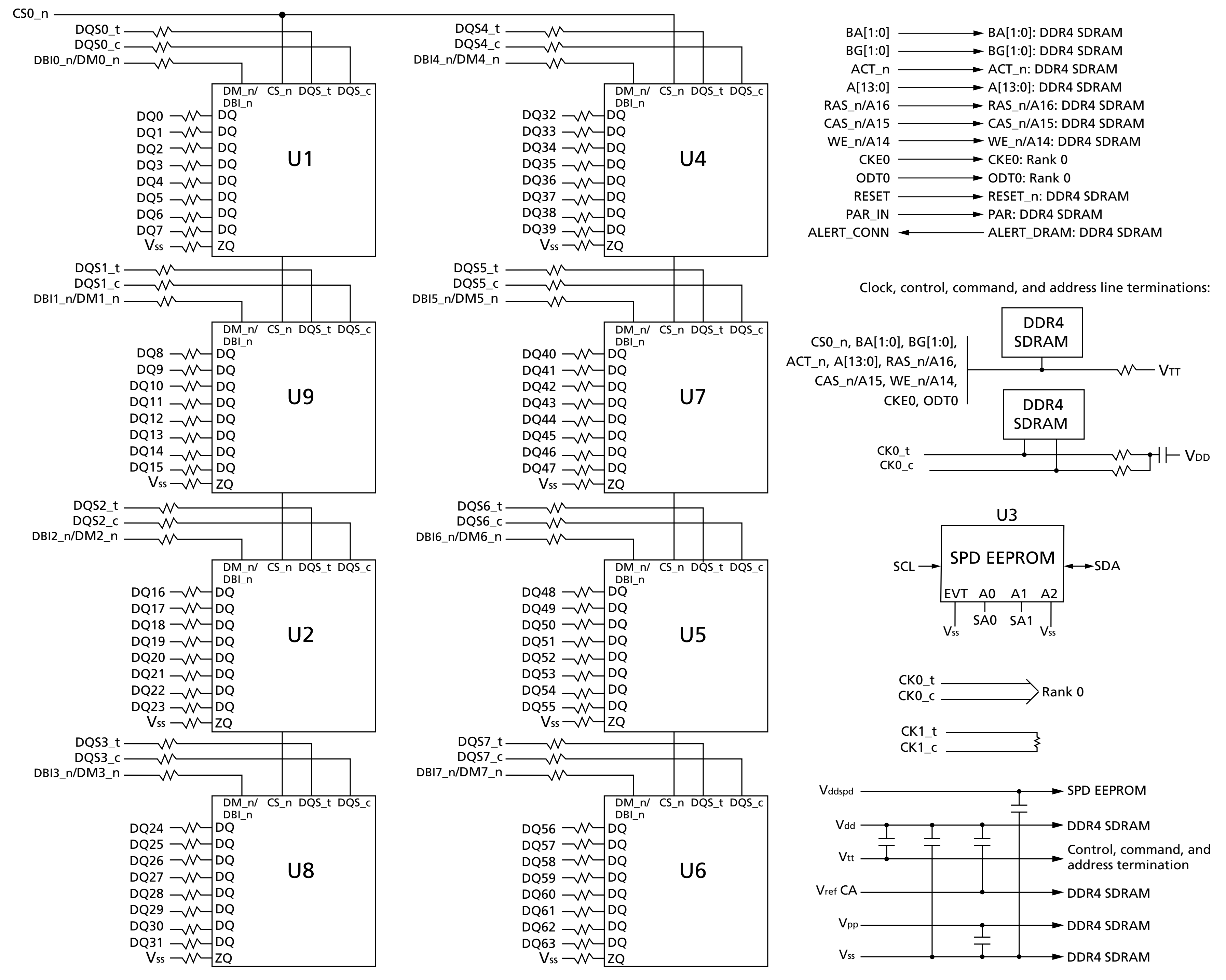

روش افزایش Rank نیز بهعنوان یکی از مهمترین روشهای افزایش حجم حافظه شناخته میشود. درشکل زیر یک ماژول Single-Rank حافظه 4GB با هشت عدد تراشه DDR4 با حجم هرکدام 4Gb(512MB) با ساختار X8 را مشاهده میکنید.

همانطور که میدانید در برخی FPGA ها، میتوان دو عدد کنترلکننده DDR پیاده کرد. با این اوصاف اگر از دو کانکتور DIMM استفاده کنیم (که به آن Double Slot میگویند)، میتوان با در نظر گرفتن Rank هرکدام، اتصال را بهصورت شکل زیر انجام داد. برای بررسی انواع دیگر اتصال یک یا دو Slot به FPGA، به برگه اطلاعات هر FPGA رجوع گردد. در بخش اول شکل زیر، یک Slot بهصورت Single Rank به FPGA متصل شده است. در بخش دوم شکل زیر، یک Slot بهصورت Dual Rank به FPGA متصل شده است. در بخش سوم تصویر، دو Slot هرکدام بهصورت Dual Rank به FPGA متصل شدهاند. در بخش چهارم، دو Slot بهصورت Single Rank به FPGA متصل شدهاند.

قطعه SPD در ماژول های DDR

در ماژولهای DIMM، یک عدد E2PROM دارای حسگر دما وجود دارد که به آن ابزار سریال پیش_شناسایی (Serial Redetect) یا SPD میگویند. این واحد وظیفه فراهم کردن دادههای مورد نیاز جهت شناسایی ماژول DDR به کنترلکننده و سیستمعامل را بر عهده دارد. دادههای موجود بر روی این حافظه شامل حجم، فرکانس، ساختار (8X و …) و همچنین CAS Latency و مواردی از ایندست هست. محتویات SPD برای ماژولهای DIMM مبتنی بر DDR3 در جدول زیر آورده شده است.

| Byte Number | Function Described | SPD Hex Values |

| 0 | DDR3-CRC RANGE, EEPROM BYTES, BYTES USED | 92 |

| 1 | DDR3-SPD REVISON | 5 |

| 2 | DDR3-DRAM DEVICE TYPE | 0B |

| 3 | DDR3-MODULE TYPE (FORM FACTOR) | 1 |

| 4 | DDR3-SDRAM DEVICE DENSITY & BANKS | 2 |

| 5 | DDR3-SDRAM DEVICE ROW & COLUMN COUNT | 12 |

| 6 | DDR3-BYTE 6 RESERVED | 0 |

| 7 | DDR3-MODULE RANKS & DEVICE DQ COUNT | 0 |

| 8 | DDR3-ECC TAG & MODULE MEMORY BUS WIDTH | 0B |

| 9 | DDR3-FINE TIMEBASE DIVIDEND/DIVISOR | 52 |

| 10 | DDR3-MEDIUM TIMEBASE DIVIDEND | 1 |

| 11 | DDR3-MEDIUM TIMEBASE DIVISOR | 8 |

| 12 | DDR3-MIN SDRAM CYCLE TIME (TCKMIN) | 0C |

| 13 | DDR3-BYTE 13 RESERVED | 0 |

| 14 | DDR3-CAS LATENCIES SUPPORTED (CL4 => CL11) (LSB) | 7C |

| 15 | DDR3-CAS LATENCIES SUPPORTED (CL12 => CL18) (MSB) | 0 |

| 16 | DDR3-MIN CAS LATENCY TIME (TAAMIN) | 6C |

| 17 | DDR3-MIN WRITE RECOVERY TIME (TWRMIN) | 78 |

| 18 | DDR3-MIN RAS# TO CAS# DELAY (TRCDMIN) | 6C |

| 19 | DDR3-MIN ROW ACTIVE TO ROW ACTIVE DELAY (TRRDMIN) | 30 |

| 20 | DDR3-MIN ROW PRECHARGE DELAY (TRPMIN) | 6C |

| 21 | DDR3-UPPER NIBBLE FOR TRAS & TRC | 11 |

| 22 | DDR3-MIN ACTIVE TO PRECHARGE DELAY (TRASMIN) | 20 |

| 23 | DDR3-MIN ACTIVE TO ACTIVE/REFRESH DELAY (TRCMIN) | 8C |

| 24 | DDR3-MIN REFRESH RECOVERY DELAY (TRFCMIN) LSB | 70 |

| 25 | DDR3-MIN REFRESH RECOVERY DELAY (TRFCMIN) MSB | 3 |

| 26 | DDR3-MIN INTERNAL WRITE TO READ CMD DELAY (TWTRMIN) | 3C |

| 27 | DDR3-MIN INTERNAL READ TO PRECHARGE CMD DELAY (TRTPMIN) | 3C |

| 28 | DDR3-MIN FOUR ACTIVE WINDOW DELAY (TFAWMIN) MSB | 0 |

| 29 | DDR3-MIN FOUR ACTIVE WINDOW DELAY (TFAWMIN) LSB | F0 |

| 30 | DDR3-SDRAM DEVICE OUTPUT DRIVERS SUPPORTED | 82 |

| 31 | DDR3-SDRAM DEVICE THERMAL & REFRESH OPTIONS | 5 |

| 32 | DDR3-MODULE THERMAL SENSOR | 80 |

| 33 | DDR3-SDRAM DEVICE TYPE | 0 |

| 34–59 | DDR3-RESERVED BYTES 34–59 | 0 |

| 60 | DDR3-MODULE HEIGHT (NOMINAL) | 3 |

| 61 | DDR3-MODULE THICKNESS (MAX) | 11 |

| 62 | DDR3-REFERENCE RAW CARD ID | 0B |

| 63 | DDR3-ADDRESS MAPPING EDGE CONNECTOR TO DRAM | 0 |

| 64 | DDR3-HEAT SPREADER SOLUTION | 0 |

| 65 | DDR3-REGISTER VENDOR ID (LSB) | 4 |

| 66 | DDR3-REGISTER VENDOR ID (MSB) | B3 |

| 67 | DDR3-REGISTER REVISON NUMBER | 3 |

| 68 | DDR3-REGISTER TYPE | 0 |

| 69 | DDR3-REG CTRL WORDS 1 AND ZERO | 0 |

| 70 | DDR3-REG CTRL WORDS 3 AND 2 | 50 |

| 71 | DDR3-REG CTRL WORDS 5 AND 4 | 55 |

| 72 | DDR3-REG CTRL WORDS 7 AND 6 | 0 |

| 73 | DDR3-REG CTRL WORDS 9 AND 8 | 0 |

| 74 | DDR3-REG CTRL WORDS 11 AND 10 | 0 |

| 75 | DDR3-REG CTRL WORDS 13 AND 12 | 0 |

| 76 | DDR3-REG CTRL WORDS 15 AND 14 | 0 |

| 77–116 | DDR3-RESERVED BYTES 77–116 | 0 |

| 117 | DDR3-MODULE MFR ID (LSB) | 80 |

| 118 | DDR3-MODULE MFR ID (MSB) | 2C |

| 119 | DDR3-MODULE MFR LOCATION ID | Variable |

| 120 | DDR3-MODULE MFR YEAR | Variable |

| 121 | DDR3-MODULE MFR WEEK | Variable |

| 122–125 | DDR3-MODULE SERIAL NUMBER | Variable |

| 126–127 | DDR3-CRC | Variable |

| 128–145 | DDR3-MODULE PART NUMBER | 18JBF25672PY-1G4DZ |

| 146 | DDR3-MODULE DIE REV | 44 |

| 147 | DDR3-MODULE PCB REV | 5A |

| 148 | DDR3-DRAM DEVICE MFR ID (LSB) | 80 |

| 149 | DDR3-DRAM DEVICE MFR (MSB) | 2C |

| 150–175 | DDR3-MFR RESERVED BYTES 150–175 | 0 |

| 176–255 | DDR3-CUSTOMER RESERVED BYTES 176–255 | FF |

- نکته: دقت شود که ولتاژ تغذیه E2PROM بانام VDDSPD شناخته شده و در مستند xr-dimm_spec_v20 برای DDR3، بین 3 تا 3.3 ولت و با توجه به مستند M4XS-AGS1QC0J-B برای DDR4 بین 2.2 تا 3.6 ولت هست. البته طبیعی است که این مقدار بسته به نوع تراشه E2PROM مورداستفاده در ماژول تغییر میکند.

در ماژولهای DIMM از نوع DDR تا DDR3 حجم این حافظه 256 Byte و در حافظههای DDR4 برابر با 512 Byte هست. این حافظه با پروتکل I2C (نوع خاصی از I2C به نام PMBus) به بیرون ماژول و کنترلکننده متصل بوده و آدرسدهی این تراشههای E2PROM بهوسیله سه پایه SA0~2 و در دو شکل زیر صورت میگیرد. در شکل اول، ارتباط کنترلکننده و E2PROM درون ماژول، با کلاک و داده مشترک در شکل دوم با کلاک و داده غیر مشترک صورت میگیرد. همانطور که دیده میشود، با این روش آدرسدهی، کنترلکننده میتواند با 8 عدد Slot از نوع DIMM ارتباط برقرار کند.

- باید تأکید کرد که SDA و SCL مذکور، در بیرون از ماژول و بر روی برد مادر باید به روشهای نشان دادهشده در دو شکل زیر، Pullup شوند و ولتاژ Pullup آنها نیز همان VDDSPD است.

- پایه Event-n در ماژولهای DIMM توسط حسگر دمایی درون تراشه E2PROM مذکور مورداستفاده قرار گرفته و از طریق آن، رخداد های دمایی به کنترلکننده اطلاع داده میشود. در صورت عدم استفاده از این پایه مبتنی بر مستند e8-MT16JSF25664HY-1G4D1 از شرکت Micron باید بدون اتصال رها گردد.

جمع بندی

در این مطلب بیان شد که برای شبیه سازی DDR باید UI سیگنال های DQ ،DQS ،Clock ،Address ،Command و Control چقدر است. روش انتخاب DDR مناسب برای تراشه کنترلر خود نیاز بیان شد. همچنین این نکته ذکر گردید که دانستن مفهوم Rank، در انتخاب روش های شبیه سازی از اهمیت زیادی برخوردار میباشد. در قسمت بعد از سلسه مباحث صفر تا صد حافظه های DDR به بررسی انواع پیکربندی سخت افزار و پیاده سازی تراشه DDR روی بورد پرداخته خواهد شد.

امیدوارم از این آموزش کمال بهره را برده باشید. در صورت داشتن هرگونه نظر یا سوال درباره این مطلب یا تجربه مشابه اون رو در انتهای همین صفحه در قسمت دیدگاه ها قرار بدید. در کوتاه ترین زمان ممکن به اون ها پاسخ خواهم داد. اگر این مطلب براتون مفید بود، اون رو به اشتراک بگذارید تا سایر دوستان هم بتوانند استفاده کنند. شما میتویند سایر مطالب من رو از این لینک و یا آدرس Linkedin من مطالعه و مورد نقد و بررسی قرار بدید. خوشحال می شم هم از طریق Comment ذیل این پست و هم از طریق Email و Linkedin با من در ارتباط باشید. همینطور میتونید این مطلب را توی اینستاگرام با هشتگ microelecom# به اشتراک بگذارید و پیج مایکروالکام (microelecom@) رو هم منشن کنید.

با تشکر از جناب مهندس موحدیان عطار