سلام به همه همراهان مایکروالکام. همون طور که در جریان هستید در این سری از مطالب سعی میکنم تمام مقدمات لازم برای طراحی و شبیه ساز حافظه های DDR را با شما در میان بگذارم. در این مطلب نکات تکمیلی طراحی شماتیک و PCB مبتنی بر حافظه های DDR و شبیه سازی آن بررسی خواهد شد. پس با من تا انتهای مطلب همراه باشید. همچنین شما میتویند سایر مطالب من رو از این لینک و یا آدرس Linkedin من مطالعه و مورد نقد و بررسی قرار بدید. خوشحال می شم هم از طریق Comment ذیل این پست و هم از طریق Email و Linkedin با من در ارتباط باشید.

مقدمه

در این بخش، واپسین نکات طراحی شماتیک و PCB برای حافظه های DDR را بیان میکنیم. مطالبی که در این قسمت به آن پرداخته خواهد شد شامل موراد زیر است:

- باقی مانده ملزومات شماتیکی ترسیم حافظه های DDR

- بررسی انواع ماژول های مبتنی بر حافظه های DDR

- انواع توپولوژی های ترسیم PCB در اتصال DDR ها به Controller

- ملاحظات جابجایی (Swap) پایه های DDR در ترسیم PCB آن

بررسی انواع پیکربندی سخت افزاری و پیاده سازی تراشه DDR بر روی برد

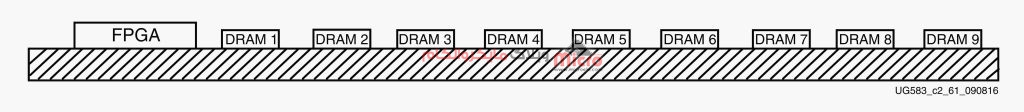

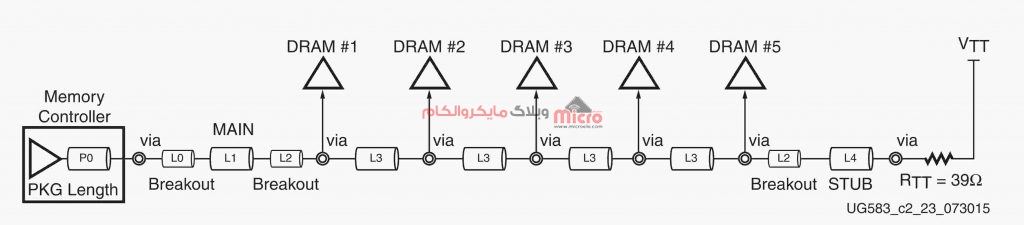

- دو ساختار کلی برای چیدمان DDR وجود دارد. ساختار حرکت جهشی”Fly By” و ساختار پوست حلزونی “Clamshell”. در ساختار Fly By، چیدمان قطعات به صورت شکل زیر است:

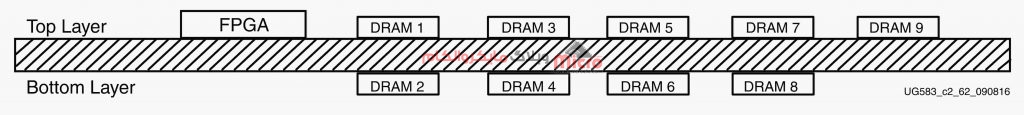

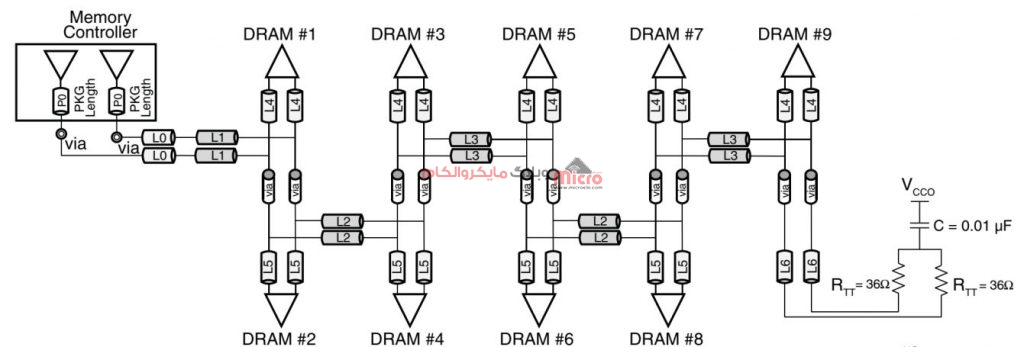

- در ساختار Clamshell، چیدمان DDR ها به صورت شکل زیراست:

توپولوژی Fly By سبب میشود که Routing ساده تر و Signal Integrity بهبود یابد ولی قیمت بورد را افزایش میدهد. توپولوژی Clamshell دارای Routing دشوارتری است ولی برای جاهایی که ابعاد بورد کوچک بوده یا مشکل جا داریم مناسبتر است. با توجه به این که DDR ها در توپولوژی Clamshell پشت به پشت هم در دو طرف بورد میآیند، جای بسیار کمی جهت Via زدن و Routing وجود دارد. لذا مطابق استاندارد JEDEC امکان Mirror کردن برخی پایههای DDR در آدرسهای آن ها وجود دارد. در جدول زیر میتوان پایههای Mirror شده در DDR4 را مشاهده کنید. بدین ترتیب، صرفاً با یک Via میتوان دو پایه آدرس را به DDRهای پشت و رو متصل نمود (پایههای BG1 و BG0 صرفاً زمانی میتوانند Mirror شوند که BG1 در تراشه موجود باشد).

| Memory Controller Pin | DRAM Pin( Non Mirrored) | DRAM Pin (Mirrored) |

| A3 | A3 | A4 |

| A4 | A4 | A3 |

| A5 | A5 | A6 |

| A6 | A6 | A5 |

| A7 | A7 | A8 |

| A8 | A8 | A7 |

| A11 | A11 | A13 |

| A13 | A13 | A11 |

| BA0 | BA0 | BA1 |

| BA1 | BA1 | BA0 |

| BG0 | BG0 | BG1 |

| BG1 | BG1 | BG0 |

توپولوژی Fly By

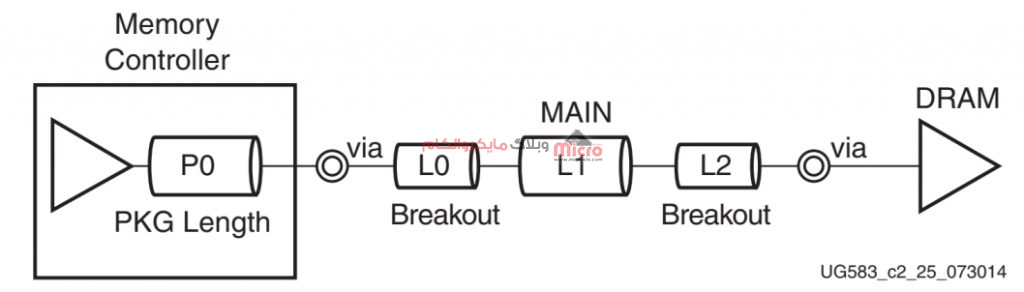

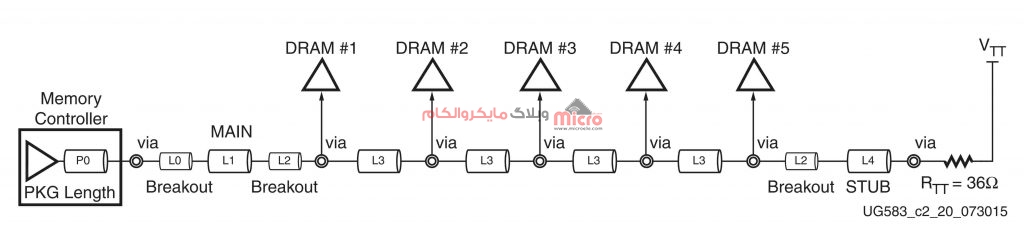

در شکل زیر میتوان نحوه اتصال Address/Command/Controll را در توپولوژی Fly By برای DDR4 دید.

ساختار Fly-By برای کلاک DDR4 مطابق شکل زیر است.

در جدول زیر میتوان امپدانس، طول و فاصله Trace کلاک را برای DDR4 در توپولوژی Clamshell مشاهده میشود.

| Parameter | L0(Device Breakout) | L1(Main PCB) | L2(DRAM Breakout) | L3 | (To R L4TT) | Units |

| Trace type | Stripline | Stripline | Stripline | Stripline | Stripline | – |

| impedance ZDIFF Clock differential |

86±10% | 76±10% | 86±10% | 90±10% | 76±10% | Ω |

| Trace width/space/width | 4.0/4.0/4.0 | 6.0/6.0/6.0 | 4.0/4.0/4.0 | 4.0/5.0/4.0 | 6.0/6.0/6.0 | mil |

| Trace length | 0.0~1.5 | 0.0~4.0 | 0.0~0.1 | 0.35~0.75 | 0~1.0 | inches |

| Spacing in address, command, and control signals (minimum) | 8.0 | 20 | 8.0 | 20 | 20 | mil |

| Spacing to other group signals (minimum) | 8.0 | 30 | 8.0 | 30 | 30 | mil |

| Maximum PCB via count per signal | 7 | – |

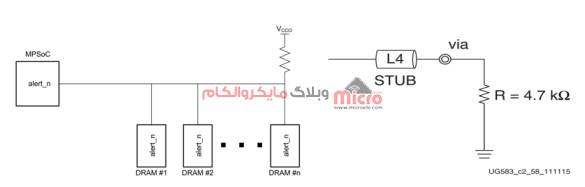

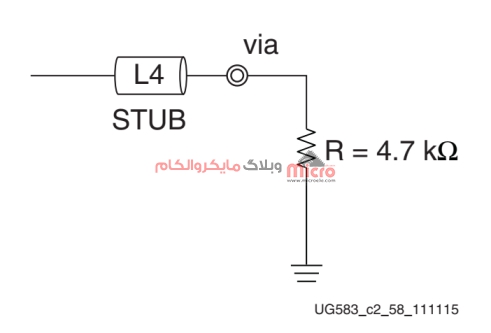

- همچنین برای Reset_n و Alert_n در ساختار Flyby به صورت شکل زیرعمل میکنیم

در جدول زیر میتوان امپدانس، طول و فاصله Trace کلاک را برای DDR4 در توپولوژی Fly By مشاهده میشود.

| Parameter | L0(Device Breakout) | L1 (Main PCB) | L2 (DRAM Breakout) | L3 | L4(To RTT) | Units |

| Trace type | Stripline | Stripline | Stripline | Stripline | Stripline | – |

| Single-ended impedance Z0 | 50±10% | 36±10% | 50±10% | 50±10% | 39±10% | Ω |

| Trace width | 4.0 | 7.0 | 4.0 | 4.0 | 6.0 | mil |

| Trace length | 0.0~1.5 | 0.0~4.0 | 0.0~0.1 | 0.35~0.75 | 0~1 | inches |

| Spacing in address, command, and control signals (minimum) | 4.0 | 8.0 | 4.0 | 8.0 | 8.0 | mil |

| Spacing to clock signals (minimum) | 8.0 | 20 | 8.0 | 20 | 20 | mil |

| Spacing to other group signals (minimum) | 8.0 | 30 | 30 | 30 | 30 | mil |

| Maximum PCB via count | 7 | – | ||||

توپولوژی Clamshell

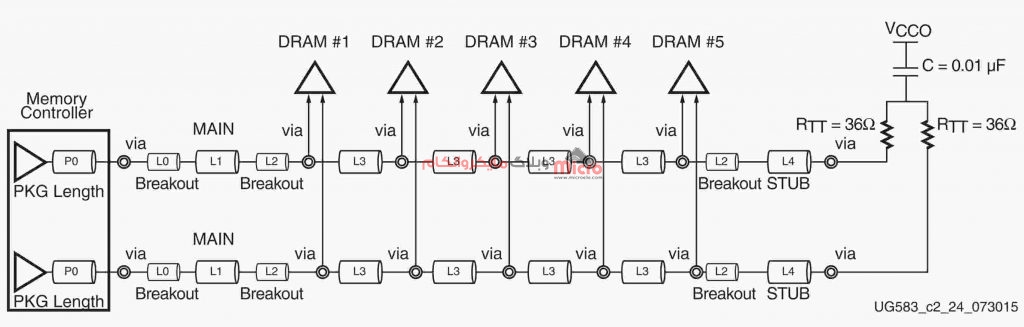

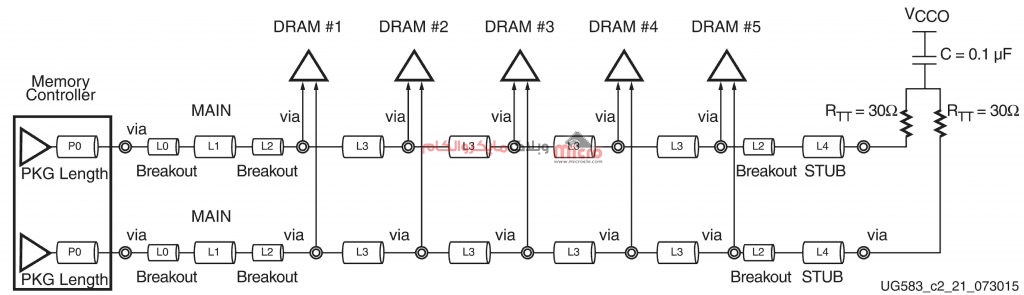

در توپولوژی Clamshell برای Address/Command/Control مبتنی بر DDR4، یک لایه جایگزین انتخاب شده و این سیگنالها را در آن توسعه میدهیم. لذا همان طور که در شکل زیر میبینیم، FPGA در لایه رو و لایههای 1، 3، 5 و 7 به عنوان لایههای سیگنالهای Address/Command/Control تراشههای موجود در لایه رو و لایههای 2، 4، 6 و 8 به عنوان لایههای سیگنالهای Address/Command/Control تراشههای موجود در لایه پشت انتخاب میشوند.

- در جدول زیر میتوان امپدانس، طول و فاصله Traceهای Address/Command/Control را برای DDR4 در توپولوژی Clamshell مشاهده میکرد.

| Parameter | L0(Device Breakout) | L1(Main PCB) | L2(DRAM Breakout) | L3 | (To R L4TT) | Units |

| Trace type | Stripline | Stripline | Stripline | Stripline | Stripline | – |

| Clock differential impedance ZDIFF |

86±10% | 76±10% | 86±10% | 90±10% | 76±10% | Ω |

| Trace width/space/width | 4.0/4.0/4.0 | 6.0/6.0/6.0 | 4.0/4.0/4.0 | 4.0/5.0/4.0 | 6.0/6.0/6.0 | mil |

| Trace length | 0.0~1.5 | 0.0~4.0 | 0.0~0.1 | 0.35~0.75 | 0~1.0 | inches |

| Spacing in address, command, and control signals (minimum) |

8.0 | 20 | 8.0 | 20 | 20 | mil |

| Spacing to other group signals (minimum) |

8.0 | 30 | 8.0 | 30 | 30 | mil |

| Maximum PCB via count per signal |

7 | – | ||||

- ساختار Clamshell برای کلاک مطابق شکل زیر است.

توضیح

در توپولوژی Clamshell برای کلاک مبتنی بر DDR4، یک لایه جایگزین انتخاب شده و این سیگنال ها را در آن توسعه میدهیم. لذا FPGA در لایه رو و لایههای 1، 3، 5 و 7 به عنوان لایههای سیگنال کلاک تراشههای موجود در لایه رو و لایههای 2، 4، 6 و 8 به عنوان لایههای سیگنال کلاک تراشههای موجود در لایه پشت انتخاب میشوند. در جدول زیر میتوان امپدانس، طول و فاصله Trace کلاک را برای DDR4 در توپولوژی Clamshell مشاهده میشود.

| Parameter | L0 FPGA Breakout |

L1 | L2 | L3 | L4 | L5 | L6 VTT Stub | Units |

| Layer (recommended) |

Upper inner |

Upper inner |

Lower inner |

Upper inner |

Top | Bottom | Bottom | |

| Differential impedance Z0 |

86 | 76 | 90 | 90 | 86 | 86 | 76 | Ω |

| Length | 0.0~1.5 | 0.0~4.0 | L3+0.2 | 0.45~0.85 | For mirrored case, L4 = L5; for non mirrored case, make as short as possible |

≤1.0 | inch | |

| Width/space/ width |

4.0/4.0/4.0 | 6.0/6.0/6.0 | 4.0/5.0/4.0 | 4.0/5.0/4.0 | 4.0/4.0/4.0 | 4.0/4.0/4.0 | 6.0/6.0/6.0 | mil |

| Spacing to addr/cmd/ctrl |

8.0 | 20 | 20 | 20 | 20 | 20 | 20 | mil |

| Spacing to other groups |

8.0 | 30 | 30 | 30 | 30 | 30 | 30 | mil |

- ساختار Fly-By و Clamshell برای داده ( DQ و DQS و DM) مطابق شکل زیر است. همچنین در جدول زیر میتوان امپدانس، طول و فاصله Traceهای داده را برای DDR4 در توپولوژی Clamshell و Fly By مشاهده میشود.

| Parameter | L0(Device Breakout) | L1(Main PCB) | L2(DRAM Breakout) | Units |

| Trace type | Stripline | Stripline | Stripline | – |

| dq single-ended impedance Z0 | 50±10% | 39±10% | 50±10% | Ω |

| dqs differential impedance ZDIFF | 86±10% | 76±10% | 86±10% | Ω |

| Trace width (nominal) | 4.0 | 6.0 | 4.0 | mil |

| Differential trace width/space/width | 4.0/4.0/4.0 | 6.0/6.0/6.0 | 4.0/4.0/4.0 | mil |

| Trace length | 0.0~1.5 | 0.0~4.0 | 0.0~0.1 | inches |

| Spacing in byte (minimum) | 4.0 | 8.0 | 4.0 | mil |

| Spacing byte to byte (minimum) | 4.0 | 20 | 4.0 | mil |

| dq to dqs spacing (minimum) | 4.0 | 20 | 8.0 | mil |

| Spacing to other group signals (minimum) |

8.0 | 30 | 30 | mil |

| Maximum PCB via count | 2 | – | ||

- در شکل زیر میتوان نحوه اتصال Address/Command/Controll را در توپولوژی Fly By برای DDR3 آمده است. همچنین در جدول زیر امپدانس، طول و فاصله Traceهای Address/Command/Control برای DDR3 در توپولوژی Fly By قابل بررسی میباشد.

| Parameter | L0(Device Breakout) | L1(Main PCB) | L2(DRAM Breakout) | L3 | (To R L4TT) | Units |

| Trace type | Stripline | Stripline | Stripline | Stripline | Stripline | – |

| Single-ended impedance Z0 | 50±10% | 36±10% | 50±10% | 50±10% | 39±10% | Ω |

| Trace width | 4.0 | 7.0 | 4.0 | 4.0 | 6.0 | mil |

| Trace length | 0.0~1.5 | 0.0~4.0 | 0.0~0.1 | 0.35~0.75 | 0~1.0 | inches |

| Spacing in address, command, and control signals (minimum) |

4.0 | 8.0 | 4.0 | 8.0 | 8.0 | mil |

| Spacing to clock signals (minimum) |

8.0 | 20 | 8.0 | 20 | 20 | mil |

| Spacing to other group signals (minimum) |

8.0 | 30 | 30 | 30 | 30 | mil |

| Maximum PCB via count | 7 | – | ||||

- برای Reset_n در ساختار Fly By به صورت شکل زیر عمل میکنیم.

- ساختار Fly-By برای کلاک DDR3 مطابق شکل زیر است.

- در جدول زیر میتوان امپدانس، طول و فاصله Trace کلاک برای DDR3 در توپولوژی Fly By مشاهده میشود.

| Parameter | L0(Device Breakout) | L1(Main PCB) | L2(DRAM Breakout) | L3 | (To R L4TT) | Units |

| Trace type | Stripline | Stripline | Stripline | Stripline | Stripline | – |

| Clock differential impedance ZDIFF |

86±10% | 76±10% | 86±10% | 90±10% | 76±10% | Ω |

| Trace width/space/width | 4.0/4.0/4.0 | 6.0/6.0/6.0 | 4.0/4.0/4.0 | 4.0/5.0/4.0 | 6.0/6.0/6.0 | mil |

| Trace length | 0.0~1.5 | 0.0~4.0 | 0.0~0.1 | 0.35~0.75 | 0~1.0 | inches |

| Spacing in address, command, and control signals (minimum) |

8.0 | 20 | 8.0 | 20 | 20 | mil |

| Spacing to other group signals (minimum) |

8.0 | 30 | 8 | 30 | 30 | mil |

| Maximum PCB via count per signal |

7 | – | ||||

برای یافتن اطلاعات دقیقتر به برگه اطلاعات قطعات DDR4 و DDR3 و مستندات مرجع طراحی PCB برای آنها رجوع گردد.

استفاده از DDR4 Modules با کانکتورهای SODIMM و DIMM و XRDIMM

در بررسیهای انجامشده مشخص شد که در ماژولهای عمومی DDR4 که وظیفه افزایش SDRAM در Main board ها را بر عهده دارند، از ساختار افزایش Rank در DDR4 استفاده شده است. لذا با اضافه کردن چند عدد پایه CS میتوان به حافظههای زیادتر دست یافت. در این رابطه، برای مثال اگر ساختار تراشههای حافظه برای ما X16 بوده و حجم آن نیز 16Gb (2GB) باشد، با 64 عدد خط داده، در هر Rank، میتوان 64Gb (8GB) حافظه به بورد اضافه کرد. لذا اگر Rank حافظه را Quad-Rank انتخاب کنیم، 256Gb(32GB) حافظه به بورد اضافه شده است.

لذا میتوان با استفاده از کانکتور SODIMM یا DIMM، یک ماژول حافظه، با ساختار تراشههای 16X و حجم حافظه 32GB را که Quad-Rank است، بهراحتی به بورد اضافه نمود.

سوالی که بهوجود میآید این است که آیا کانکتورهای SODIMM و DIMM، تستهای لرزش و شوک فیزیکی را با موفقیت پشت سر میگذارد؟

در تستهایی که بر روی این کانکتورها انجام شده است، گواه بر این است که این کانکورها استاندارد تست شوک 50-MIL-STD-202G Method 213B و استاندارد تست لرزش 50-MIL-STD-202G Method 214A را با موفقیت پشت سر گذاشته اند. علاوه بر این، در برگه اطلاعات کانکتورهای SODIMM، به استاندارد JESD22-B-102 در مونتاژ و قابلیت لحیمکاری، استاندارد J-STD-020C در مقاومت حرارتی حین مونتاژ و تستهای مکانیکی لرزش و شوک توسط سازنده نیز اشاره کرده و موفقیت آنها را تصدیق میکند.

به سبب این که تستهای انجام شده بر روی خود کانکتور بوده و ماژول حافظه SODIMM در آن قرار داده نشده است، نمیتوان به قطع یقین اعلام کرد که این کانکتورها به همراه ماژول نصبشده بر روی آن، قابلیت پشتسر گذاردن تستهای شوک و ویبره را دارند. تحت این شرایط، ماژولهایی به بازار صنایع با شرایط دشوار (نظامی و صنعتی) وارد شده است که با نامهای XRDIMM و RDIMM شناخته میشود. در ادامه به بررسی بیشتر آنها میپردازیم.

معرفی ماژولهای مبتنی بر حافظه DDR

در برخی از کاربردها به دلیل کمبود جا بر روی بورد و یا به دلایل مختلف تجاری، نیازمند افزایش و کاهش حافظه بر روی بردها هستیم تا آن را برای خواست مشتری و یا شرایط و نیازمندیهای کاری خاصی آماده کنیم. این امر مستلزم استفاده از ساختارهای ماژولار بر روی بورد میباشد. عمومیترین ساختار ماژولار برای حافظههای DDR، استفاده از انواع کانکتورها و ماژولهای DIMM است. در جدول زیر به برخی از آنها اشاره میشود.

| نام ماژول | ویژگی | شکل ماژول |

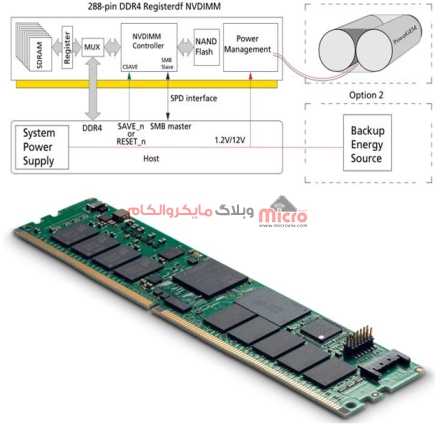

| NVDIMM | دارای حافظه Flash و خازنهای Backup که برق را برای DDR تا 72 ساعت تأمین کرده و با قطع طی این مدت، برق دادهها از بین نمیرود. |

|

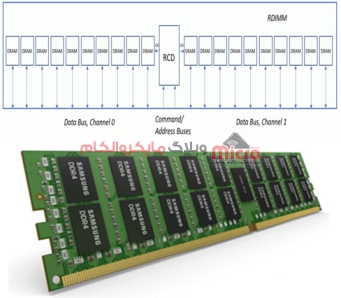

| RDIMM | یک رجیستر بر سر راه آدرس و کلاک وجود دارد که ابتدا آن را رجیستر میکند و بعد بر روی DRAM میفرستد. لذا دیگر نیازی به رجیستر داده توسط کنترلر نیست. |

|

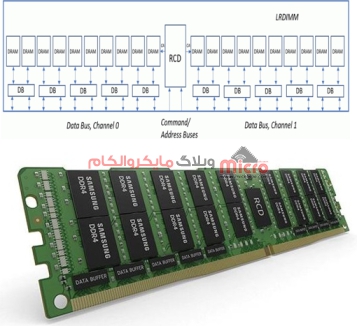

| LRDIM | ساختار همان ساختار RDIMM است با این تفاوت که برای DQ ها DQS های هر تراشه نیز یک بافر قرار داده است. |

|

| VLP RDIMM | همان RDIMM است با این تفاوت که ابعاد کوچکتری دارد و برای اتاق های سرور و کاربرد های کم جا مورد استفاده قرار میگیرد. |

|

| UDIMM یا به اختصار DIMM | همان RDIMM است ولی بدون رجیستر |

|

| Mini RDIMM و VLP Mini RDIMM و Mini UDIMM | همان ماژولهای بالا در ابعاد کوچکتر و Dencity بیشتر. تعداد پایه این ماژول ها نسبت به SODIMM ها بیشتر است. دلیل تعداد پایه بیشتر نیز قابلیت اطمینان بالاتر در کاربردهای مخابراتی است. |

|

| SOUDIMM یا همان SODIMM | SODIMM با ابعاد کوچک و تعداد پایههای کم برای کاربردهای چگال و فشرده همچون لپ تاپ |

|

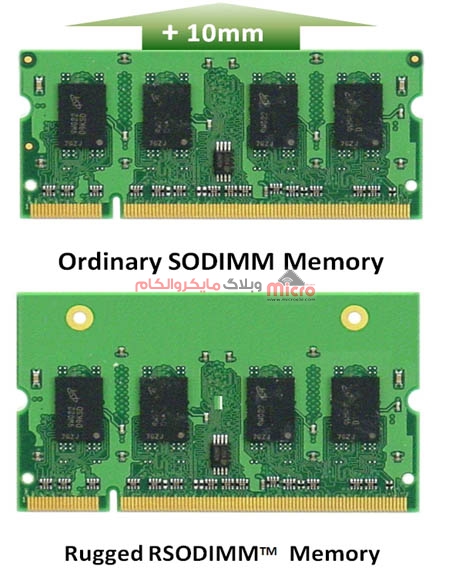

| RSODIMM | همان SODIMM است که عرض آن افزوده شده و دو عدد جای پیچ به آن اضافه شده است. لازم بذکر است که کانکتور آن همان کانکتور SODIMM است. مهمترین مزیت آن قابلیت استفاده برای کاربردهای شرایط سخت و تست شوک و ویبره است و عیب عمده آن نیز عدم امکان ایجاد پشته (non Stackable) با آن است. (ابعادی که در شکل میبینید، برای ماژول DDR3 است) |

|

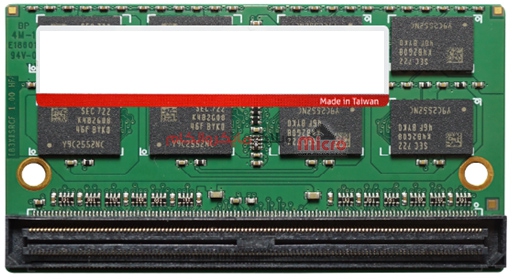

| XRDIMM | کانکتور این نوع کاملاً متفاوت با SODIMM و DIMM بوده و در زیر بورد قرار دارد. علاوه بر آن دارای دو جا پیچ بوده که آن را برای کاربردهای شرایط سخت و تست شوک و ویبره مناسب میسازد. به دلیل قرارگیری پیچ ها در محل مناسب، امکان پشتهسازی آن ها نیز وجود دارد. (ابعادی که در شکل میبینید، برای ماژول DDR3 است) |

|

همانطور که در دیده میشود با توجه به مزایای XRDIMM مانند ابعاد کوچک، گذراندن موفقیتآمیز تست شوک و ویبره، امکان پشتهسازی و کاهش فضای موثر آن بر روی بورد مادر، این ماژول انتخاب اول در بین تمام دیگر انواع ماژولهای مبتنی بر DDR میباشد.

برای دریافت استاندارد ها و Pinout ساختار XRDIMM می توانید بطور مستقیم از طریق وبلاگ و یا ایمیل و LinkedIn با من در تماس باشید.

ملاحظات Swap پایهها در شماتیک DDR4 با در نظر گرفتن Length match

ابتدا به تعریف عبارت “گروه بایت” که بارها در این بخش مورد استفاده قرار میگیرد، میپردازیم. گروه بایت درواقع همان Byte Lain است، ولی به جهت تطبیق با مستندات مرجع، با این نام قید شدهاست. در ساختار X4، گروه بایت شامل چهار بیت پشت سر هم که یک DQS دارند میشود. مثلا بیتهای Q0 تا Q3 یک گروه بایت هستند ولی Q2 تا Q5 با وجود این که پشت سر هم هستند، یک گروه بایت نیستند چرا که DQS آنها یکسان نیست.

همچنین در ساختارهای X8 و X16، گروه بایت شامل هشت بیت پشت سر هم که یک DQS دارند میشود (لذا Q0 تا Q7 یک گروه بایت هستند ولی Q5 تا Q11 با وجود این که پشت سر هم هستند، یک گروه بایت نیستند چرا که دارای DQS یکسان نیستند). ملاحظات زیر در Swap پایههای مربوط به تراشه های DDR4 الزامیست.

- پایههای داده، آدرس و کنترل همگی میتوانند در گروه بایت مربوط به خودشان Swap شوند. این برای DQS ها استثناء است و DQS ها الزاماً باید به پایه های از پیش تعیینشده متصل گردند. با توجه به این که برای ساختارهای X8 و X16 به هر 8 بایت یک عدد DQS تعلق میگیرد، لذا برای اتصال Byte Lane به یک دسته از پایههای FPGA لازم است پایههای DQS حافظه به یکی از انواع DBC یا QBC و یا GC پردازنده (با این اولویت که ابتدا GC، اگر موجود نبود QBC و در نهایت اگر هیچ کدام موجود نبود حتما به DBC)، متصل گردند.

- بیت های داده داخل هر گروه بایت بدون محدودیت میتوانند با یکدیگر Swap شوند. به تعریف گروه بایت دقت شود.

- پایههای آدرس و کنترل حافظه، برای اتصال به FPGA، در یک گروه بایت شناختهشده و در محل اتصال به بانک های درنظر گرفته شده برای DDR، بدون محدودیت میتوانند بین یکدیگر Swap کنند.

- هیچگونه Swap بین پایههایی که قید نشده است، امکانپذیر نیست.

- اگر بخواهیم طراحی برای XRDIMM به گونهای باشد که ماژولهای DDR مبتنی بر هر سه ساختار X4 و X8 و X16 را بتوان بر روی آن وصل کرد، باید Length Match را بر اساس X16 انجام داد (یعنی هر 16 بیت موجود در گروه بایت و DQS ها و DM های مربوط به آنها را با هم Length Matching کرد) و Swapping را طبق ساختار X4 انجام داد. یعنی صرفاً اجازه Swap در بین بیتهای موجود در یک گروه بایت چهارتایی X4 را داریم.

- مهمترین موضوع در طراحی XRDIMM و یا ماژول مبتنی بر DDR با ساختار X16 این است که هیچ تفاونی بین آن با X8 وجود ندارد و صرفاً تنها تفاوت این است که هر تراشه DDR دارای دو جفت DQS و دو عدد DM میباشد. به همین سبب باید Length match بین گروه بایتهای 8 تایی صورت گیرد. همچنین اجازه Swap نیز صرفا بین گروه بایتهای 8 تایی داده میشود.

- اگر بخواهیم طراحی برای XRDIMM به گونهای باشد که ماژولهای DDR مبتنی بر هر دو ساختار X8 و X16 را بتوان بر روی آن وصل کرد، باید Length Match را بر اساس X16 انجام داد. یعنی هر 8 بیت موجود در گروه بایت و DQS ها و DM های مربوط به آنها را با هم Length Matching کرد و Swapping را طبق ساختار X8 انجام داد. این بدان معنا است که صرفاً اجازه Swap در بین بیتهای موجود در یک گروه بایت هشتتایی X8 را داریم.

جمع بندی

در این قسمت، آخرین نکات لازم برای طراحی شماتیک و PCB حافظه های پرسرعت DDR بیان شد. تقریبا نکته خاصی در زمینه طراحی و اصول این حافظه ها و ساختار داخلی آن ها باقی نمانده که در چهار قسمت اخیر، به آن اشاره نشده باشد. همچنین تمام ماژول های مرسوم مبتنی بر DDR را بطو کامل معرفی شد. در بخش آینده، تلاش میکنم طراحی یک مجموعه DDR3 را برای اتصال به یک FPGA بطور مثال از صفر تا صد با همدیگر انجام داده تا بطور کامل روال را ببینید و آماده ارائه بخش شبیه سازی این حافظه ها در نرم افزار Hyperlynx شوید.

امیدوارم از این آموزش کمال بهره را برده باشید. در صورت داشتن هرگونه نظر یا سوال درباره این مطلب یا تجربه مشابه اون رو در انتهای همین صفحه در قسمت دیدگاه ها قرار بدید. در کوتاه ترین زمان ممکن به اون ها پاسخ خواهم داد. اگر این مطلب براتون مفید بود، اون رو به اشتراک بگذارید تا سایر دوستان هم بتوانند استفاده کنند. شما میتویند سایر مطالب من رو از این لینک و یا آدرس Linkedin من مطالعه و مورد نقد و بررسی قرار بدید. خوشحال می شم هم از طریق Comment ذیل این پست و هم از طریق Email و Linkedin با من در ارتباط باشید. همینطور میتونید این مطلب را توی اینستاگرام با هشتگ microelecom# به اشتراک بگذارید و پیج مایکروالکام (microelecom@) و LinkedIn من رو هم رو هم mention کنید.