سلام به همه همراهان مایکروالکام. همون طور که در ابتدای بخش قبل گفتم، این مباحث طولانی و بسیار پیوسته هستند. لذا دنبال کردن مطالب تا رسیدن به آخرین نقطه طراحی و شبیه سازی مجموعه حافظه DDR در نرم افزار Hyperlynx، صبر زیادی میطلبد. البته بسیار هم شیرین هست. پس با من تا انتهای مطلب همراه باشید. همچنین شما میتویند سایر مطالب من رو از این لینک و یا آدرس Linkedin من مطالعه و مورد نقد و بررسی قرار بدید. خوشحال می شم هم از طریق Comment ذیل این پست و هم از طریق Email و Linkedin با من در ارتباط باشید.

ادامه ساختار داخلی DDR، قوانین طراحی شماتیک DDR و اتصال آن به FPGA

در بخش قبل، مقدماتی در مورد ساختار داخلی و فرمول های محاسباتی لازم در شبیه سازی DDR ها پرداخته شد. در این بخش، به بررسی ساختار حافظه DDR، دسته سیگنالهای خروجی آن، ارتباط این سیگنالها با یکدیگر و نحوه اتصال آنها به کنترلکننده حافظه (علیالخصوص FPGA ها) بررسی شده و ملزومات آن بیان میشود. بعد از مطالعه این بخش، شما قادر به طراحی صحیح شماتیک پروتکل ارتباطی DDR خواهید بود.

تفاوت DDR3 و DDR4

تفاوت بین DDR3 و DDR4 در ولتاژ کاری، فرکانس کاری و توان مصرفی بوده ( که در بخش قبل مفصلا به آن پرداخته بودم و پیشنهاد میکنم آن را مطالعه کنید) و عملا تفاوتی در پیکربندی این دو ساختار وجود ندارد. لذا (بجز در مواردی که تفاوت بنیادین در پیکربندی، اتصالات سخت افزاری و قوانین وجود دارد و به آن اشاره شده است)، میتوان قوانین و ساختار مشابهای را اتخاذ نمود.

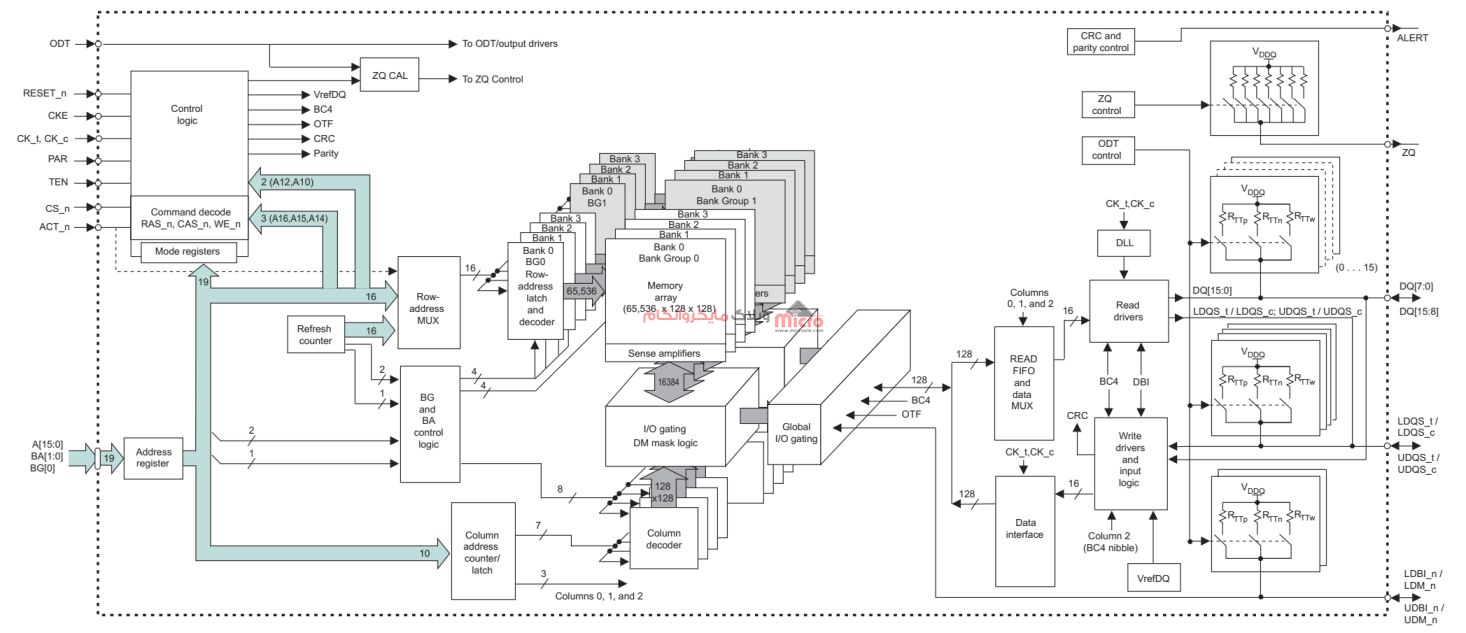

ساختار داخلی حافظه DDR در سطح Block Diagram

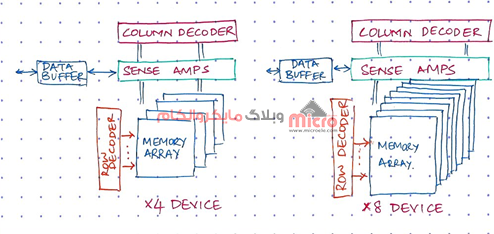

برای درک بهتر اندازه حافظه و انتخاب قطعه حافظه مناسب، لازم است ساختار داخلی SDRAM DDR را بشناسیم. در شکل زیر ساختار DDR (در یکی از معمولترین حالات 4X) مشاهده میکنید. همینطور که میبینید، آدرس و Command به صورت یک باس به تمام گروه_بانکها داده میشود. در عوض دادهها از هر گروه_بانک به صورت جداگانه بر روی باس داده قرار داده میشوند.

خواندن و نوشتن در حافظه

برای خواندن حافظه، یک آدرس فراهم میکنیم و برای نوشتن بر روی آن از آدرس جداگانهای استفاده میکنیم. این آدرس فراهم شده توسط کاربر را در اصطلاح آدرس محلی (Local Address) میگوییم. آدرس محلی در لایه فیزیکی تبدیل به آدرس گروه_بانک، بانک، سطر و ستون میگردد که به آن در اصطلاح آدرس فیزیکی (Physical Address) میگوییم. این آدرس است که در واقع مشخصکننده منطقهای از حافظه است که میخواهیم آن را بخوانیم یا روی آن بنویسیم این ساختار در شکل زیر قابل مشاهده است.

این چیزی است که در هر بانک میبینیم:

- منطقه حافظه بانک (Memory Arrays)

- تشخیص اختصاص دهنده ردیف (Row Decoder)

- تشخیص اختصاص دهنده ستون (Column Decoder)

- تقویتکننده تشخیص (Sense Amplifiers)

برخی توضیحات

DDR, DDR2, DDR3 و حافظه DDR4 با ظرفیتی در محدوده 2~16 GB به 2 ساختار دسته بدنی میشود. در فرایند خواندن، بخش تشخیص ردیف در آدرس فیزیکی، آن ردیف از حافظه که مورد نظر کاربر است را هدف قرار میدهد و فعال میکند. این ردیف را خط کلمه (word Line) میگوییم. فعالسازی آن سبب خواندن این سطر و قراردادن آن در بخش تقویتکننده تشخیص میشود. سپس بخش Column Decoder، قسمت مورد نظر از word Line که در بخش Sense Amplifiers قرار گرفته را میخواند.

عرض ستون را bit Line میگوییم. این bit Line استانداردی دارد که X8, X4 و X16 را تشکیل میدهد که مشخصکننده bit Line با عرض 4bit و 8bit و 16bit است. عرض داده DQ هم به اندازه عرض bit Line است. لذا میتوان به بیان سادهتر گفت که عرض DDR به اندازه عرض باس DQ است.

- ساختار X16 شامل 2 عدد گروه_بانک است که هریک داری 4 عدد بانک میباشد.

- ساختار X4 و X8 شامل 4 عدد گروه_بانک که هریک شامل 4 عدد بانک میباشد.

بررسی دو ساختار مطرح شده

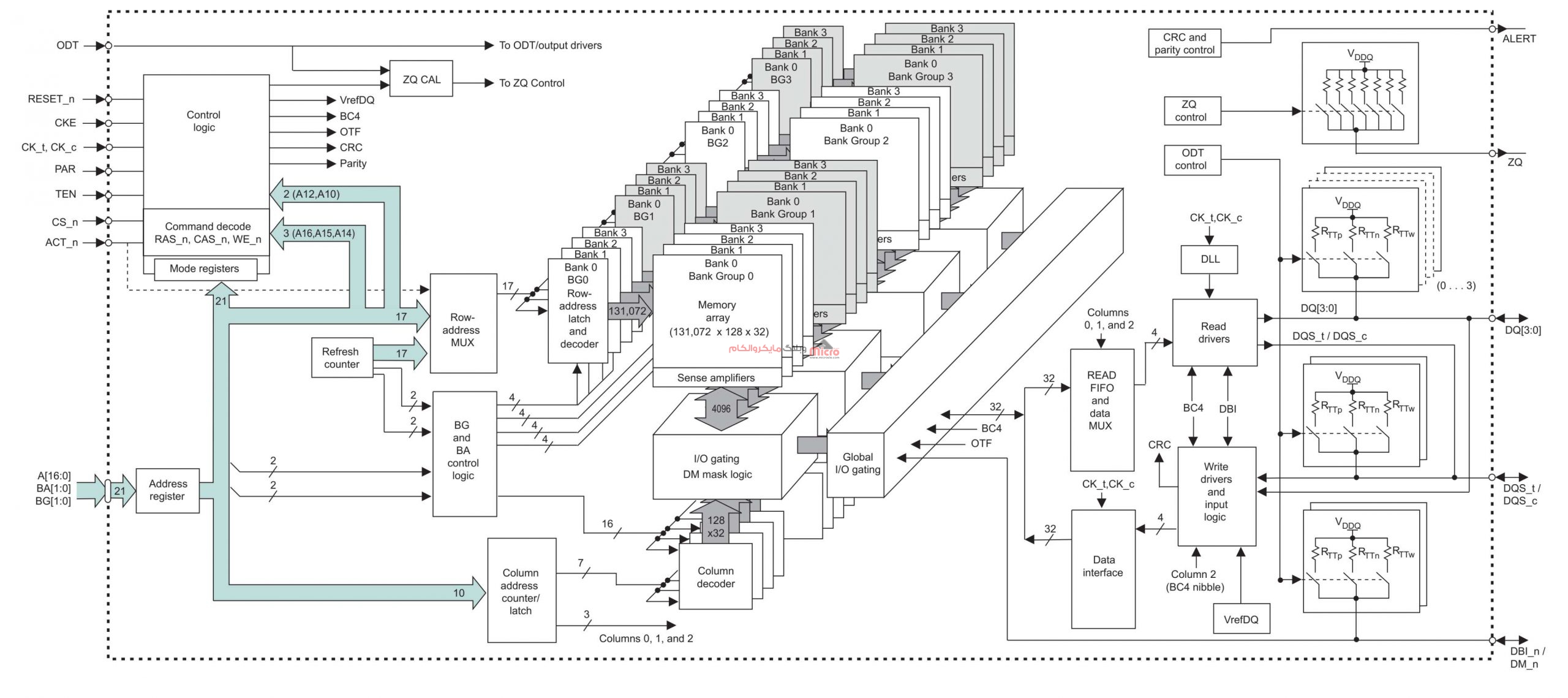

در زیر به بررسی این دو ساختار و تفاوت بین آنها میپردازیم. در شکل زیر یک نمونه حافظه 8Gb(2 Gig X4) را مشاهده میکنید. همانطور که دیده میشود، 4 خط DQ وجود دارد که میتوان گفت عرض DDR4 زیر 4 است یا به عبارتی این DDR از نوع X4 است و چون حجم آن در برگه اطلاعات قطعه برابر با 8Gb ذکر شدهاست، لذا هر گروه_بانک دارای حجم 2Gb است. ضمنا همانطور که دیده میشود، تعداد زوج DQS-n/p هم برابر با 1 بوده که برای تنها Byte Lane با عرض 4 خارجشده از حافظه میباشد.

بررسی یک حافظه 8Gb

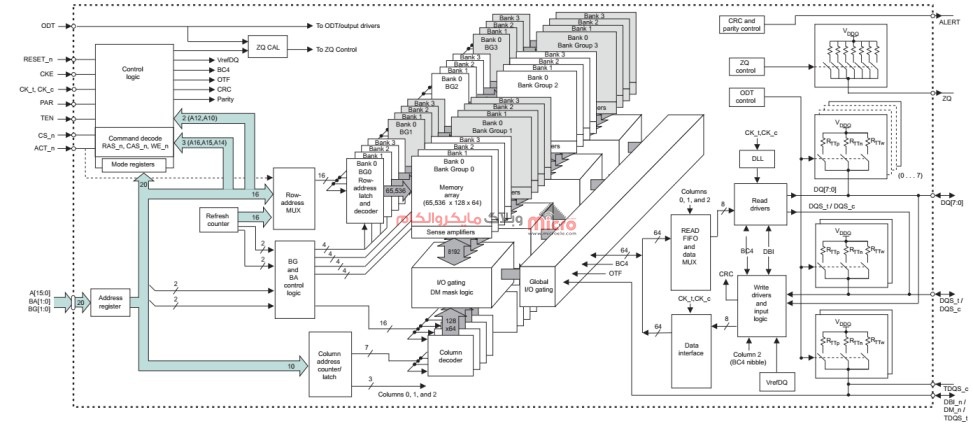

در شکل زیر یک نمونه حافظه 8Gb (1 Gig X8) را مشاهده میکنید. همانطور که دیده میشود، 8 خط DQ وجود دارد که میتوان گفت عرض DDR زیر 8 است. به عبارتی این DDR4 از نوع X8 است و چون حجم آن در برگه اطلاعات قطعه برابر با 8Gb ذکر شده است، لذا هر گروه_بانک دارای حجم 1Gb است. همانطور که دیده میشود، تعداد زوج DQS-n/p برابر با 1 است که برای یک Byte Lane با عرض 8 خارجشده از حافظه میباشد.

بررسی یک حافظه 8Gb دیگر

در شکل زیر یک نمونه حافظه 8Gb(512 Meg X16) را مشاهده میکنید. همانطور که دیده میشود، 16 خط DQ وجود دارد که میتوان گفت عرض DDR زیر 16 است یا به عبارتی این DDR از نوع X16 است و چون حجم آن در برگه اطلاعات قطعه برابر با 8Gb ذکر شده است، لذا هر گروه_بانک دارای حجم 256Meg است. ضمنا همانطور که دیده میشود، تعداد زوج DQS-n/p هم برابر با 2 بوده که برای دو Byte Lane با عرض 8 خارجشده از حافظه میباشد.

با توجه با موارد ذکر شده در مورد ساختار پایهها و ارتباط بین آنها، دستهبندی فیزیکی سیگنالهایی که در PCB و شماتیک در یک گروه قرار میگیرند به صورت زیر است:

- دسته دادههای موجود در هر Byte Lane؛ شامل DQها و DQS-n/p آن Byte Lane بخصوص

- دسته آدرس و Command و کنترل: شامل تمام خطوط آدرس، WE،CAS ،RAS ،CLK-p/n ،CLE،ACT_B،TEN،PAR ،RESET،ODT و CS

ساختار پایهها و کاربرد آنها در DDR

حافظههای DDR4 دارای بانکهای حافظه هستند که هر چند عدد از این بانکها را در یک گروه_بانک (Bank-Group) قرار میدهند. این قابلیت به حافظههای DDR کمک میکند که خواندن، نوشتن و Refresh را بطور جداگانه در هر دسته از گروه_بانکها مستقلاً انجام دهند. این قابلیت پهنای بانک و بازدهی حافظه را افزایش میدهد.

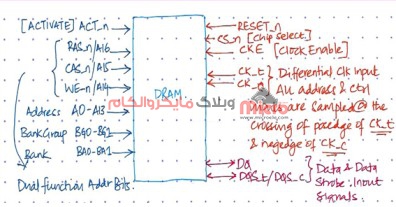

آگاهی در مورد سیگنالهایی که خصوصیات مشترک و روابط بین آنها، الزامات سختافزاری ( مثل Net list و Length matching) را به طراحی شماتیک تحمیل میکنند، ضروری است لذا در اینجا به برخی از پایهها و کاربرد آنها در حافظه میپردازیم. این پایهها کامل نیستند ولی غالب سیگنالهایی را که در حافظه مشاهده میکنید را شامل میشوند. در شکل زیر برخی سیگنالهای مشترک در حافظه DDR را مشاهده میکنید.

همچنین در جدول زیر توضیحات و عملکرد این پایهها شرح داده شده است.

| Symbol | Type | Function |

| Reset-n | Input | DRAM تنها زمانی ACTIVE است که این پایه High باشد. |

| CS-n | Input | DRAM تنها زمانی به سایر پایههای خود نگاه میکند که این پایه LOW باشد. |

| CKE | Input | Clock Enable.

فعالساز کلاک، پایهای که سیگنال کلاک داخلی و بافر ورودی و درایورهای خروجی را فعال میکند. |

| CK-t/CK-c | Input | Differential clock inputs.

کلاک دیفرانسیلی ورودی، پایهای که تمام سیگنالهای آدرس و کنترل، برای سنکرون بودن, با لبه بالارونده آن (CK-t) و لبه پایین رونده (CK-c) کار میکنند. |

| DQ/DQS | Inout | پایههای باس داده و پایههای سیگنال DQS که در واقع سیگنال data strobe است. DDR و DDR2 دارای DQS تک مسیره هستند. ولی DDR3 و DDR4 دارای differential data strobes هستند که کار کلی آن کاهش نویز سویچینگ همزمانی و بهبود crosstalk سیگنالهای خروجی و ورودی حافظه میباشد که این کار را با بهبود Timing انجام میدهد. |

| RAS-n/A16 | Input | پایههای دو کاربرده در DDR4

زمانی که ACT-n و CS-n پایین هستند، این پایهها در حالت بیتهایی از آدرس قرار میگیرند. زمانی که ACT-n بالا باشند، این سیگنالها به عنوان Command بکار گرفته میشوند و کاربرد اصلی آنها در فرایند خواندن و نوشتن و سایر Command ها است. در DDR4 پایههای RAS#, CAS# و WE# با پایههای Address به صورت Share در آمدهاند. |

| CAS-n/A15 | ||

| WE-n/A14 | ||

| ACT-n | Input | پایه فعالساز Command |

| BG0-1 | Input | پایههای انتخاب گروه بانک و آدرس بانک |

| BA0-1 | ||

| A0-13 | Input | ورودیهای آدرس |

برخی ویژگیهای حافظه DDR4 و DDR3

- فرکانس کلاک DDR3 در حدود 400MHz–1066MHz و نرخ انتقال داده آن در حدود 800MT/s-2133MT/s است.

- فرکانس کلاک DDR4 در حدود 800MHz-2400MHz و نرخ انتقال داده آن در حدود 1600MT/s-3200MT/s است.

- ولتاژ کاری DDR4 در محدود 2V است.

- ولتاژ کاری DDR4 در محدود 5V است.

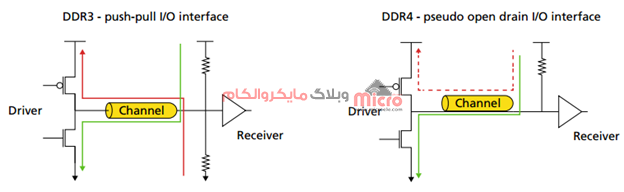

- DDR4 از یک IO Interface جدید تحت عنوان Pseudo Open Drain 1.2V (POD12) استفاده میکند این اینترفیس هم مصرف توان را کاهش داده و هم SI را بهبود میبخشد (منظور از SI همان Signal Integrity است که در بخش های شبیه سازی در آینده در مورد آن صحبت می کنیم). شکل زیر تفاوت Push-pull IO را برای DDR3 و DDR4 با هم مقایسه میکند.

- DDR4 ها دارای دو مد برای built-in error detectionمیباشند.

- Cyclic redundancy cycle (CRC) که برای داده استفاده میشود.

- Parity checking که برای آدرس و Command استفاده میشود.

- برای اینکه مباحث Signal Integrity رعایت شود باید خطوط ADDR/CMD/CTRL با توپولوژی Fly-By در PCB روت شوند (بطور کلی سه توپولوژی یا ساختار در طراحی PCB و شماتیک DDR ها وجود دارد: Fly-By، Clam-Shel و T-Topology. این سه ساختار و تفاوت های آن ها در بخش سوم توضیح داده خواهد شد). البته این روش سبب ایجاد Skew بین کلاک و DQS میشود که با استفاده از Write Leveling در DDR4 مرتفع خواهد شد. DDR3 و DDR4ها دو خط کلاک دارند که برای کلاک address و command به حافظه داده میشود.

- علاوه براین، حافظه از این کلاک برای تولید سیگنال DQS در DLL استفاده میکند.

- DDR, DDR2و DDR3 دارای پایههای command به نامهای CS# و RAS#, CAS#, WE#, CKE, ODT هستند. بعضی ساختارهای خاص DDR3 دارای پایههای RESET#, PAR_IN (1.5V LVCMOS I/O standard), ERR_OUT# (SSTL-15 I/O standard) هستند.

- DDR4پایههای اضافهتری نسبت به خانوادههای قبلی به نامهای ACT# (activate) pin و BG (bank group) دارد. بسته به ساختار حافظه و کاربرد آن، پایههای PAR (address command parity) و ALERT# نیز میتوانند در آن موجود باشند.

- بسته به عرض Interface برقرار شده، سیگنال DQS میتواند در گروههای X4 و X8 (بسته به نوع حافظه و نوع DIMM)عمل کند. پیکربندی X4 و X8 برای Capture داده ورودی از یک زوج دیفرانسیلی DQS و DQS-n استفاده میکند. لذا برای ساختارهای 16X نیاز به زوج دیفرانسیلی UDQS-p و USQS-n (برای بایت بالایی) و زوج دیفرانسیلی LDQS-p و LSQS-n (برای بایت پایینی) است.

- سیگنال DQ در هنگام خواندن از حافظه، با لبه سیگنالهای DQS همراستا شدهاند و در هنگام نوشتن در حافظه نیز با مرکز آن همراستا شدهاند. همراستایی با مرکز که ذکر شد، با شیفت -90 درجهای سیگنال DQS توسط حافظه انجام میشود.

- حافظه، زمانهای setup (Tds) و hold (Tdh)را برای همراستایی سیگنالهای DQ و DM براساس لبه سیگنال DQS نتظیم میکند.

- SDRAM از سیگنال DM در حین نوشتن استفاده میکند پایینکشیدن این پایه به معنی این است که نوشتن روی SDRAM مورد قبول است. SDRAM در صورتی که سیگنال DM بالا نگه داشتهشده باشد، سیگنال DQ را MASKمیکند. جهت تولید سیگنال DM توصیه میشود گه از سیگنال DQ در یک گروه با DQS استفاده شود تا Skew به حداقل خود برسد.

- در DDR4 همچون سایر SDRAMها، DM پشتیبانی میشود؛ با این تفاوت که در DDR4 سیگنال DM به صورت active LOW و bidirectional است؛ چراکه از Data Bus Inversion (DBI) به وسیله همان پایه پشتیبانی میکند. DBI با DM مالتیپلکس شدهاند و به همین دلیل امکان استفاده از هر دو به صورت همزمان نیست. لذا DBI دقیقا معکوس DM عمل میکند و زمانی که LOW است، در هنگام نوشتن بر روی حافظه، داده Invert شده و در DDR4 ذخیره میگردد و اگر DBI به صورت High باشد، داده Invert نمیشود و به صورت مستقیم در DDR4 ذخیره میگردد (در مورد DBI در بخش اول بطور مفصل توضیح داده شده است).

- سیگنالهای error correction coding (ECC) در برخی از DDR4های 72-bit تعبیه شدهاند که نسبت به حافظههای 64-bit، پایههای اضافهتری دارند و کاربرد آن پایههای اضافی اصلاح خطا در ارسال داده است. پایههای هشتگانه ECC اضافی این SDRAMها باید به گروه DQS یا DQ موجود single بر روی FPGA وصل شوند.

- با بررسی ارتباط بین این پایهها مشخص است که این پایهها از نظر ویژگیهای سختافزاری (اندازه و ابعاد trackهای متصل به آنها و دیگر مسائل فیزیکی) در یک دسته قرار میگیرند. این دستهبندی در این مستند با نام دستهبندی فیزیکی شناخته میشود. در ادامه دستهبندیهای فیزیکی پایهها به تفکیک بیان میشود.

قوانین اتصال DDR3 و DDR4 به FPGA

برای اتصال پایههای DDR4 به FPGA باید قوانین خاصی را رعایت نمود.

- منظور از Address/Control/Command، سیگنالهای CS-n, RAS-n, CAS-n, WE-n, ba, bg, CLK-n/p, CKE, ODT, ACT-n, و PAR میباشند.

- پایههای موجود در یک Byte lane در FPGA بصورت N0 تا N12 شمارهگذاری میشوند. در هر بانک موجود درFPGA، تعداد 4 عدد Byte Lane تحت عنوان T0~T3 وجود دارد. لازم بهذکر است که هر Byte Lane به دو بخش بالایی و پایینی تحت عنوان L و U تقسیم میگردد (T0L,T0U). 6 عدد TL و 7 عدد TU که در هر دو بخش دو تا از پایهها مر بوط به DBC میباشند.

این قانونها بشرح زیر است

- در ساختارهای DDR4 و DDR3 که به صورت X8 و X16 هستند، سیگنال DQSn/p باید به زوج کلاک موجود در Byte Lane تراشه FPGA، در قسمت U(یعنی پایههای N6 و N7) قرارگیرد (در کلیه تراشههای Ultra Scale، این پایهها چه از نوع DBC باشد و چه از نوع QBC، این اصل صادق است.). همچنین سیگنالهای DQ تراشه DDR4 متناظر با همان DQSn/p، باید در همان Byte Lane در پایههایی غیر از N1 و N12 قرار گیرند.

- در ساختارهای DDR4 که به صورت X16 هستند، سیگنال DQSn/p یک قانون جدید وجود دارد (که برای DDR3 وجود ندارد) و آن این که اگر LDQDn/p و UDQSn/p روی تراشه حافظه با ساختار X16 داشته باشیم، LDQSn/p ها به پایههای DQS زوج و UDQSn/p ها به پایههای DQS فرد وصل میشوند. یعنی مثلا اگر دو تراشه DDR4 با ساختار X16 داشتیم که LDQDn/p و UDQSn/p داشتند، و خواستیم به بانک صفر وصلشان کنیم، LDQSn/p تراشه اول به DQS0n/p، UDQSn/p تراشه اول به DQS1n/p، LDQSn/p تراشه دوم به DQS2n/p و در نهایت UDQSn/p تراشه دوم به DQS3n/p وصل میکنیم. دادههای DQ هر کدام از DQS ها را نیز به همین ترتیب وصل میکنیم.

مثلا در شکل زیر، میتوان این پیکربندی را دید.

- سیگنال DM/DBI باید به پایه N0 در Byte Lane متناظر متصل گردد.

- سیگنالهای DQS در تراشههای DDR4 با ساختار 16X، برای باس با چند تراشه DDR4، باید به این ترتیب وصل شوند:

- زوج DQSLn/p تراشه DDR4 شماره یک، به DQS0n/p

- زوج DQSUn/p تراشه DDR4 شماره یک، به DQS1n/p

- زوج DQSLn/p تراشه DDR4 شماره دو، به DQS2n/p

- زوج DQSUn/p تراشه DDR4 شماره دو، به DQS3n/p

- زوج DQSLn/p تراشه DDR4 شماره سه، به DQS4n/p

- زوج DQSUn/p تراشه DDR4 شماره سه، به DQS5n/p

و به همین ترتیب ادامه پیدا میکند. در شکل زیر، برای یک تراشه موجود در باس با ساختار Fly By این اتصال را مشاهده میکنید.

برخی توضیحات

این موضوع محل قرارگیری فیزیکی Byte Lane ها را محدود نمیکند. Byte Lane ها بسته به روتینگ سادهتر در PCB میتوانند به همراه DQSn/p مربوط به خود جابجا شوند. اگر برای تراشه 16X با خط داده 32 بیتی بخواهیم یک نقشه اتصال پایه به یک بانک خاص از FPGA در نظر بگیریم، میتوانیم مطابق جدول زیر عمل کنیم.

| Bank-Byte | Selected Memory Data Bytes |

Allocated DQS (in IP on FPGA) |

Memory Device Mapping |

| BankX_BYTE3 | DQ[0-7] | DQS0 | Memory Device 0 – LDQS |

| BankX_BYTE2 | DQ[8-15] | DQS1 | Memory Device 0 – UDQS |

| BankX_BYTE1 | DQ[16-23] | DQS2 | Memory Device 1 – LDQS |

| BankX_BYTE0 | DQ[24-31] | DQS3 | Memory Device 1 – UDQS |

- بطور کلی در ساختارX16، سیگنالهای DQL ،DQSL و DML به یک Byte Lane متصل شده و DQH ،DQSH و DMH به Byte Lane بعدی وصل میگردد.

- پایههای N1 و N12 میتوانند به عنوان Addr/Ctrl استفاده شوند.

- هیچیک از پایههای داده (DQS, DQ, DM) نباید در Byte Lane ای قرار گیرند که در آن سیگنالهای Addr/Ctrl وجود دارد.

- DM های مربوط به هر Byte Lane تراشه DDR، باید به پایه N0 موجود در Byte Laneتراشه FPGA قرار گیرد که بقیه ی پایههای Byte Laneتراشه DDR در آن واقع است. دقت شود که در ساختار X4 پایه DM استفاده نمیشود و باید باید پایه آن بر روی تراشه DDR با مقاومتی برابر با مقاومت Traceهای DQ (که عموماً بین 40 تا 50 اهم است)، به زمین متصل گردد.

- برای DDR هایی با ساختارهای مبتنی بر X4، پایههای DQS تراشههای حافظه باید به همراه پایههای DQ چهار گانه داده خود قرار گیرند. محل قرارگیری آن ها در بانک FPGA نیز برای Nibble پایین، پایههای N0 و N1 هر Byte Lane و برای Nibble بالا، پایههای N6 و N7 هر Byte Lane تراشه FPGA است. نکته مهم این است که Nibble بالا و پایین، در یک Byte Lane از FPGA واقع شوند و ترتیب آنها هم به این صورت باشد که Nibble بالا به Nibble بالا و Nibble پایین به Nibble پایین Byte Lane وصل گردد.

- برای DDR های مبتنی بر ساختار X8 و X16، پایههای DQS تراشه های حافظه باید به همراه پایههای هشت گانه DQ داده خود قرار گیرند. محل قرارگیری آن ها در بانک FPGA نیز پایههای N6 و N7 هر Byte Lane تراشه FPGA است.

- تراشههای X4 باید به صورت زوج مورد استفاده قرار گیرند و استفاده تعداد فرد آن امکان پذیر نیست.

- پایههای Addr/Ctrl باید حتماً در یک بانک قرار گیرند.

- پایه VRP که برای DCI استفاده میشود باید با استفاده از مقامت 240 اهم به زمین متصل شود (این امر برای تراشههای Ultra Scale برقرار بوده و برای سایر خانوادهها باید مورد بررسی قرار گیرد).

- پایه CK از DDR4 باید به پایههای DBC یا QBC از Byte Lane بالایی متصل شود ( باید به بانکی وصل شود که برای آدرس و کنترل استفاده شده است).

- پایه reset-n میتواند به هریک از بانکهای مختص به DDR4 متصل گردد.

- یک بانک میتواند بین دو کنترلر به صورت مشترک استفاده شود ولی هر کنترلر باید از Byte Lane مختص خود استفاده نماید.

- همه IO Bank های استفاده شده برای DDR4 باید در یک ستون (در ساختار داخلی FPGA) قرار داشته باشند.

- پایههای DDR4 باید حتماً به بانکهای متوالی (در ساختار داخلی FPGA) متصل باشند.

بیانی دیگر

به طور خلاصه دو مورد سابق بدین معنی است که همه IO Bank های استفاده شده برای DDR4 باید “مجاور” باشند. در مورد DDR4 برای مجاورت تعریف کمی خصوصیتر نیز میگردد و در بانکهای مورد استفاده برای DDR4 باید به صورت واقعی (عددی) هم مجاور بوده و Super Logic ای بین آنها وجود نداشته باشد. برای اتصال حافظههایی با ساختار 16X و 8X، باید در هر Byte Lane از FPGA، ساختار موجود در جدول زیر رعایت شود.

| I/O Type | Byte Lane | Pin Number | Signal Name |

| – | T0U | N12 | – |

| N | T0U | N11 | DQ[7:0] |

| P | T0U | N10 | DQ[7:0] |

| N | T0U | N9 | DQ[7:0] |

| P | T0U | N8 | DQ[7:0] |

| DQSCC-N | T0U | N7 | DQS0_c |

| DQSCC-P | T0U | N6 | DQS0_t |

| N | T0L | N5 | DQ[7:0] |

| P | T0L | N4 | DQ[7:0] |

| N | T0L | N3 | DQ[7:0] |

| P | T0L | N2 | DQ[7:0] |

| DQSCC-N | T0L | N1 | – |

| DQSCC-P | T0L | N0 | DM0/DBI0 |

اگر بخواهیم پیکربندی پایهها برای هر سه ساختار 16X و 8X و 4X سازگار باشند، بایددر هر Byte Lane از FPGA، ساختار موجود در جدول زیر رعایت شود.

| I/O Type | Byte Lane | Pin Number | Signal Name |

| – | T0U | N12 | – |

| N | T0U | N11 | DQ[3:0] |

| P | T0U | N10 | DQ[3:0] |

| N | T0U | N9 | DQ[3:0] |

| P | T0U | N8 | DQ[3:0] |

| DQSCC-N | T0U | N7 | DQS0_c |

| DQSCC-P | T0U | N6 | DQS0_t |

| N | T0L | N5 | DQ[7:4] |

| P | T0L | N4 | DQ[7:4] |

| N | T0L | N3 | DQ[7:4] |

| P | T0L | N2 | DQ[7:4] |

| DQSCC-N | T0L | N1 | –/DQS9_c |

| DQSCC-P | T0L | N0 | DM0/DBI0/DQS9_t |

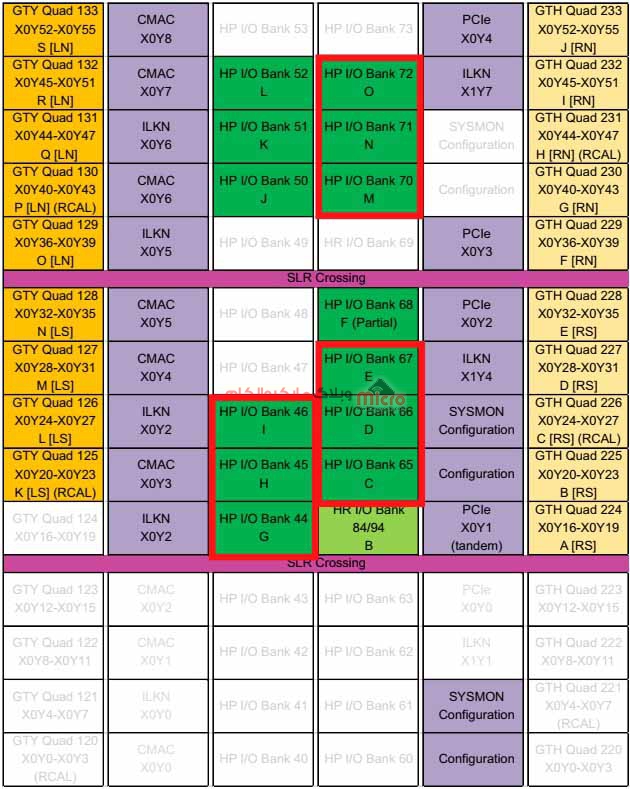

مثالی برای درک بهتر مفهوم مجاورت در بانک های FPGA

برای مثال در زیر برای این که بتوانیم FPGA های FLGB2104 را به جای یکدیگر مونتاژ کنیم (لذا باید بانکهای مشترک بین FPGA های دارای این Package انتخاب شود) باید بانکهای مورد انتخاب آن از نوع HP باشد ( تا تداخل ولتاژی با DDR4 پیدا نکند) و مجاورت این بانکها در تمام FPGA های این Package نیز رعایت شده باشد.

اگر ساختار X16 را انتخاب کنیم (این بستگی به نوع DDR4 مورد استفاده دارد که در بالا مفصل توضیح داده شد)، برای باس داده DDR4 نیاز به 16 خط داده داریم. چون 4 عدد DDR4 را جهت اتصال به باس با ساختار Fly By انتخاب کردهایم، لذا نیاز به 64 خط داده برای کل چهار DDR4 داریم. این امر حدود 2.5 بانک از بانکهای FPGA را تسخیر میکند. لذا برای اتصال این باس و باس Address/Control، حدود سه عدد بانک از FPGA را نیاز داریم. Package بالا چهار FPGA زیر را در Vertex Ultra Scale+ دارا است:

- XCVU160

- XCVU190

- XCVU9P

- XCVU11P

دسته بانک برای اتصال Fly By

سه دسته بانک برای اتصال Fly By چهار عدد تراشه DDR4 به FPGA انتخاب میشوند و شروط مجاورت که در بالا ذکر شد را در این سه دسته بررسی میکنیم.

- بانکهای 70 و 71 و 72

- بانکهای 44 و 45 و 47

- بانکهای 65 و 66 و 67

بیانی دیگر

همانطور که دیده میشود، بانکهای 70 و 71 و 72 قابل استفاده نیستند. چرا که در بانکهای XCVU11P با Super Logic از هم جدا و از مجاورت خارج شدهاند. همچنین بانکهای 44 و 45 و 47 علیرغم مجاورت در سایر تراشهها، چون در بانکهای تراشه XCVU11P موجود نیستند، قابل استفاده نیز نیستند. ولی بانکهای 65 و 66 و 67 در تمام تراشهها موجود و در تمام آنها نیز سه شرط لازم برای مجاورت را دارند. لذا برای DDR4 با قابلیت تغییر تراشه FPGA قابل استفاده هستند.

- کلاک مرجع برای DDR4 باید به پایههای GC از بانکی متصل شوند که برای DDR4 استفاده شده است.

- پایه VREF در بانکهای مختص به DDR4 باید با استفاده از مقاومت 500 اهم به زمین متصل شوند البته در EVAL از مقاومت 1 کیلو اهم استفاده شده است.

- همه پایههای DDR4 حتماً باید به یک نوع بانک متصل شوند مثلاً HR و یا HP البته در مورد کلاک مرجع و reset-n این محدودیت وجود ندارد.

- در EVAL پایه reset-n با استفاده از مقاومت 1 کیلو اهم به زمین متصل شده است.

- در EVAL پایه TEN با استفاده از مقاومت 499 اهم به زمین متصل شده است.

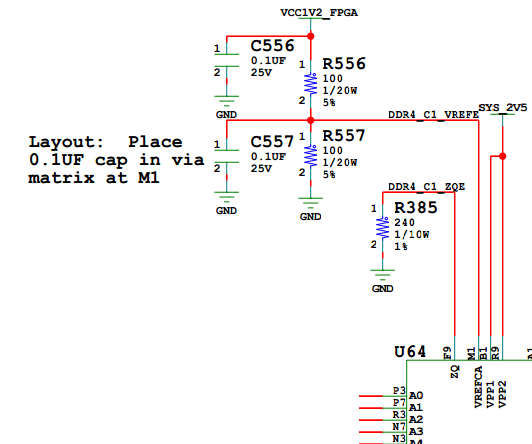

- مطابق شکل cdv در DDR4، پایه VREFCA با استفاده از تقسیم مقاومتی به تغذیه 1.2 ولت متصل میشود و پایه ZQ با مقاومت 240 اهم به زمین متصل میگردد.

جمع بندی

در این مطلب به بررسی قوانین اتصال DDR ها به FPGA پرداخته شد و مباحث مربوط به مجاورت در FPGA ها و ضرورت انتخاب بانک های مجاور را در این کنترلر عمومی و پرکاربرد بیان گردید. در بخش بعدی به بررسی روش انتخاب DDR مناسب و فاکتور های مهم در این انتخاب پرداخته خواهد شد.

امیدوارم از این آموزش کمال بهره را برده باشید. در صورت داشتن هرگونه نظر یا سوال درباره این مطلب یا تجربه مشابه اون رو در انتهای همین صفحه در قسمت دیدگاه ها قرار بدید. در کوتاه ترین زمان ممکن به اون ها پاسخ خواهم داد. اگر این مطلب براتون مفید بود، اون رو به اشتراک بگذارید تا سایر دوستان هم بتوانند استفاده کنند. شما میتویند سایر مطالب من رو از این لینک و یا آدرس Linkedin من مطالعه و مورد نقد و بررسی قرار بدید. خوشحال می شم هم از طریق Comment ذیل این پست و هم از طریق Email و Linkedin با من در ارتباط باشید. همینطور میتونید این مطلب را توی اینستاگرام با هشتگ microelecom# به اشتراک بگذارید و پیج مایکروالکام (microelecom@) رو هم منشن کنید.